# Department of Computer Science

### Analysis of Bridging faults in Double BJT BiCMOS Circuit

Sankaran M. Menon, Yashwant K. Malaiya, Anura P. Jayasumana

Technical Report CS-93-124

September 28, 1993

### Colorado State University

## Analysis of Bridging faults in Double BT BCMOS Grouit \*

Sankaran M. Menon Yashwant K. Malaiya <sup>‡</sup> Anura P. Jayasumana

Dept. of Electrical Engineering

<sup>‡</sup>Dept. of Computer Science

Glorado State University

Fort Gllins, CO 80523

#### **Abstract**

Combining the advantages of CMOS and hipdar, BiCMS is energing as a rajor technical for may high performed digital and nixed signal applications. Recent incestigations have revealed that bridging faults can be a rajor failure mode in I.G. This paper presents effects of bridging faults in BCMS circuits. Bridging faults between logical units without feedback and logical units with feedback are considered. Several bridging faults can be detected by maintaining the power supply current (I DDQ maintaining). Effects of bridging faults and bridging resistance on output logic levels have been examined along with their effects on mise immity

<sup>\*</sup>This research was supported by a SDIO/IST funded project monitored by ONR.

#### 1 Introduction

```

Combining the advantages of CMOS and Bipdar, BiCMOS is energing as a major technology for many

ligh performance dejital and nixed signal applications. The main advantages of CMOS technology

over hipdar are lower power designation and higher packing density. Bipdar technology offers better

output current drive, switching speed I/O speed and analog capability. Collining the advantages of

bindar and CMOS. Bi CMOS offers the following advantages [1]

]; imposed speed over CMOS, lower power

dssipation corpored to hipdar, flexibility in I/O (TTL, ECL, CMOS corportibility), high performance

analog capability and latch up immity. Commend to the CMOS contemports, BiCMOS circuits can

be faster by a factor of upto two for the same level of technology. Access times of less than 10 is have

been reported for 0.8 \(\mu\)mBi CMOS ECL inpt/outpt 256K and 1M-bit SRAMs [2]

]. BiCMOS is even

being considered for high performance increprocessors and dynamic RAMs, and it is felt that it will be

].

one of the main technologies to drive almost all functions in the decade alread [3]

Most of the defects and failures in present day integrated circuits can be abstracted to shorts and

opens in the intercorrects and degradation of devices [4]

]. Transistor level shorts and opens noted many

of the physical failures and defects in IG [5]

]. A study by Gailiay [6]

] on 4-bit MOS increprocessor

clips revealed that many of the faults were shorts and opens at the transistor level. Analysis of faults

in dementary static storage dements suggest that transistor level testing provides a higher coverage of

]. Thus, it is necessary to study the effects of failures at the

faults compared to that at the gate level [7]

]. The major fault models at transistor

transistor level and develop accurate fault nodels at this level [5]

level are stuck-at faults, and shorts and goess of transistors and interconnects [8]

]. It has been shown [9

that the stuck-at more does not cover many of the manufacturing defects in BiOMOS devices and that

most open faults manifest themselves as delay faults.

Rapid advances, increasing condexities and shrinking device geometries in VLSI have enabled com-

plex integrated directs to be manifactured for extremly complex systems at lower costs. Various modes

of failures can occur in such complex VLSI devices, where bridging faults have been shown to be about

half of the faults in QMOS circuits [10]

]. Another study [11]

], based on layout level defects using statistical

data fronfabrication process conducts that bridging faults can be unto 30\% of all faults. Hence, bridging

is an important failure mode which needs careful and systematic analysis. Bridging faults have long been

regarded as a possible failure mode in digital systems [12]

, B, H]. Detailed examinations of bridging

faults in nMOS/CMOS have been presented in [15]

, 16]. Effects of stuck-on and open of transistors in

ECL OR/NOR gate and 2-level complex ECL gates were presented in [17]

, 18]. Bridging faults can occur

```

Figure 1: A D-BJT Bi CMOS Nand.

within an integrated direct or a printed direct board during number turing or at a later stage. Most of the literature on bridging faults assumes a simple gate level model.

The nost command type of BiCMOS circuits employ bipdar transistans to perform the function of diving output loads and CMOS to perform togic functions. In this paper, we birefly review the operation of a double BJT (D-BJT) BiCMOS NAND device. In this paper, we present the effects of birding faults and birding resistances on output logic levels and device current (I DDQ) is examined along with their effects on mise immity.

This paper is againzed as follow. The operation of a basic BiCMOS NAND is explained in section 2. Section 3 deals with bridging within a logic element. Sections 4 and 5 cover bridging of logical rodes without feedback and with feedback respectively. Finally conducious drawnfronthe study are given in section 6.

#### 2 D-BJT BiCMOS device

```

A Dathe BJT Bi CMOS NAND realization is shown in Figure 1. The functioning of the Bi CMOS NAND

can be explained by first applying logic '0' to one or both of the inputs which would cause at least one

P-device to be ON and at least one N-device in each serial N-pairs to be OFF. With at least one N-device

in each serial N-pairs being OFF, no current is suplied to the base of Q

_2 resulting in transister Q

2 being

_1 and _2 ON, the base of the bipdar NPN transistor would be about

OFF. With the P-devices (P)

5V suplying base current and turning ON the bipdar transistor providing logic '1' at the output. With

either of the inputs being at logic '0' and the other input at logic '1' would still cause either of the parallel

carrected P-devices to be ON and either of the series carrected N-devices to be OFF. This would still

suply be current to the hipdar transistor Q

1 causing logic '1' at the output. With both the imputs at

logic '1', the P-devices (P

_1 and P _2) would be turned OFF, and the N-devices N

_1, N_2, N_3 and N_{-4} wildbe

_2 which discharges the load. Transistor N

_1 and N _2 drawcurrent

turned ON, surlying base current to Q

from the base of Q

1 this rapidy turning this device OFF. This will cause the output to be a logic '0'.

This the circuit realizes the NAND function. It may be noted that the static power consumption of the

circuit is regligible reglecting reverse biased leakage currents. A D-BJT BiCMOS gate consists of CMOS

p and nexts to perform logic function and two atput BJTs for driving the atput mee.

D-BJT BiCMOS devices do not have the full \,V\,

DD to Grandlegic swing of CMOS devices. The atput

OL) is limited to V = DD - V_{BE(Q2)}.

_{OH}) is limited to V _{DD}-V_{BE(Q1)} and output Lowedtage (V

High vdtage(V)

\frac{dV_{out}}{dV_{in}} = -1 \text{ pints}

V_{ILmax} and V_{IHmin} were determined to be 2.2\mathrm{V} and 2.7\mathrm{V} respectively, by finding the

[19, 20] on the voltage characteristics. The logic levels for BiCMOS are 0.6V to 2.2V for logic level '0' and

2.7\mathrm{V} to 4.4\mathrm{V} for logic level '1' [21]

]. Any voltage between 2.2V and 2.7V is considered in determinate. The

are V_{IHmin}=2V, V_{OHmin}=2.4V,

device daracteristics given for Fujitsu Bi (MOS) gate array devices [22]

V_{II,ma} = 0.8 \text{V} \text{ and } V_{OI,ma} = 0.5 \text{V}.

Major causes of bridging faults are related to the manifecturing defects. In the photolithography

```

Major cases of bridging faults are related to the manifacturing defects. In the plotdithography stages of the manifacturing process, diffraction and provinity are the primescore of excess metal causing bridging faults. Imprities and diffusion of metal are other sources responsible for such faults. Effects of input and output bridging faults in BiCMOS devices are examined for hard bridging with varying resistances. The following definitions are used in this paper.

Figure 2: D-BJT Bi CMOS output bridging fault (Hard short).

#### 3 Bridging within a logic element

#### 4 Bridging of logical nodes without feedback

In this dass of bridging faults, bridging of logical input and output rooks of logic elements are considered.

Bridging can be either hard bridging or the bridging can exhibit significant resistance. The effects of bridging under hard bridging and for bridging with significant resistance are given in this section for D-BJT BiCMOS devices.

Figure 3: D-BJT Bi CMOS output bridging fault (Hard short).

#### 4.1 Hard bridging faults in D-BJT BiCMOS

In this subsection we assume hard shorts for bridging faults under consideration. In CMOS, the effects of bidging can be nothed by taking into account the resistances of the paths and bidging corrections [15]. Consider a hard short between two D-BJT BiCMOS output invertees as shown in Figure 2. When  $_{1}$  and V  $_{2}$  are same, i.e., 00 or 11, then there is no direct path from Vthe logic levels at nodes VDD to ground and hence, the same logic levels, i.e., 00 or 11, are mintained. Considering the case when one of the nodes is at logic level ligh (1) and the other node is at logic level low (0). A path is created between  $V_{DD}$  and ground leading to enhanced IDDO. Such output bridging faults in BiCMOS can be detected using power supply current maintaing (I)DDQ mitaring). Since a hard short is assumed for the bridging fault, voltage levels appearing at node V1 is the same. as the voltage level appearing at mole V $_{2}$   $(V_{1}\,=\,V_{2})$  . Consider the condition where V1 is at logic level  $_1$  ON) and  $V_2$  is at logic level '0' (transistor Q  $_2'$  ON). With the output bridging fault '1' (transister Q  $_{1}$  and Q  $_{2}^{\prime}$  are the same, the output settles under consideration and since the parameters of transistons Q $_{OH}/2 = \approx 2.2 \mathrm{V}$ ), for input vectors A B = 0 1 and 10 as at one-half of the output high ('1') logic level (VDD to ground, enhanced I DDQ values are discreted shown in Figure 3. Since there is a direct path from V for output hard bridging faults. Hence, current maintaing (IDDQ) techniques can be implemented to detect such faults.

In a mitile el network, an imput bridging fault can be analyzed similarly by considering the bridging

#### 4.2 Output bridging with varying resistances

Since bridging is not a deliberate feature, it may not always be a hard short and in general may exhibit a significant resistance. A very high resistance may imply a bridging fault of no consequence. The range of values exhibiting significant impact on the logic values is investigated.

Consider the two BiCMOS at put stages as shown in Figure 4 with unknown bridging resistance  $R_X$ . When the logic levels at  $V=_1$  and  $V=_2$  are same, i.e., 00(11), then there is no direct path from  $V=_{DD}$  to ground, leading to the same logic levels, i.e., 00(11) being maintained at  $V=_1$  and  $V=_2$ . When one of the mades is at logic level 'High' (1) and the other node is at logic level 'Low' (0) with a bridging resistance of a significant value ( $R=_{X}>0\Omega$ ), the output logic levels at  $V=_1$  and  $V=_2$  needs to be studied. Spice similation of the BiCMOS output bridging fault was due for varying bridging resistances ( $R=_{X}>0\Omega$ ) and the output logic levels for both the mades  $V=_1$  and  $V=_2$  plotted are shown in Figure 5. The inference

- (1) Note  $V_{-1}$  and  $V_{-2}$  remain at  $\approx V_{-OH}/2$  ( $\approx 2.2 \mathrm{V}$ ) for bidging resistance  $R_{-}$   $X < \approx 3\Omega$ . Output level of  $\approx 2.2 \mathrm{V}$  is classified as logic level '0' for BiCMOS devices. However, the nodes  $V_{-}$  and  $V_{-2}$  exhibit degraded mise immity for these bidging resistances.

- (2) Note  $V_2$  remains at logic level '0' for all bridging resistances. However, mise immity of the node  $V_2$  is degrated for lower bridging resistance values.

drawnfronthis similation is as follows:

Figure 7: Noi se i mmuni ty of node<sub>2</sub> Winder S-BJT Bi CMOS output bri dgi ng fault.

- (3) For bridging resistances  $\geq \approx 3\Omega$  and  $\leq \approx 40\Omega$ , the logic level for node V 1 is in the 'Undefined level. Though the atput logic level is in the 'Undefined level, current minimizing can be used to detect this bridging.

- (4) When bridging resistance is greater than  $\approx 40\Omega$ , the bridging is of no consequence at the logic level.

Estination of mise immitty for both the modes were carried out. The voltage level obtained at the two modes  $(V=_1 \text{ and } V=_2)$  under varying bridging resistances were obtained. Noise immitty for 'High' logic level was estinated by counting the difference between the mode voltage and V IHmin (Minimmit put voltage for logic level 'High'). Similarly, mise immitty for 'Low' logic level was estinated by counting the difference between V  $ILma_{-x} \text{ (Maximmit put voltage for logic level 'Low')} \text{ and the mode voltage}.$

Node  $V_{-2}$  remains at logic level 'L' irrespective of the bridging resistance. The mise immitty of this note is lighly degraded at lowbridging resistances. Figure 7 show mise immitty for note V

2 under

Figure 8: Noise immunity of node Winder S-BJT Bi CMOS output bridging fault.

'Low logic level conditions. Degraded noise immity at low bridging resistance can be seen in Figure 7. As the output bridging resistance increases, the noise immity of node V  $_2$  increases. Figure 8 show noise immity for node V  $_1$  under 'High' logic level condition. It can be seen that under high bridging resistance, the logic level stags on the correct side (logic level 'H'). As the value of the bridging resistance is lowered ( $\approx 40\Omega$ ), the noise immitty of the node V  $_1$  for logic level 'High' keeps getting lower until noise immity becomes zero. Further lowering the value of bridging resistance causes the node V  $_1$  to be at an undefined level. Containing the process of lowering the value of the bridging resistances (below  $\approx 3\Omega$ ) results in logic level 'Low' at the node V  $_1$  which is a faulty logic level with a very low noise immity ( $\approx 0.006V$ ), hence cannot be seen on the plot. A logic device bring diven by this node may interpret this faulty logic level correctly.

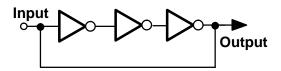

#### 5 Bridging of logical nodes with feedback

This dass of bridging faults deals with logical modes deriving its logic value from nother due to bridging. If the feedback loop does not contain docked storage derents, then asyndroms feedback paths are frequently introduced transforring continuous block into an asyndroms sequential circuit. It has been shown that if a feedback loop contains an odd number of inversions, then oscillations can occur [28]. The aroundous behavior seen in this dass of bridging faults depends on propagation delay rise time fall

].

Figure 9: Feedback bridging across odd number of D-BJT Bi CMOS inverters.

time as well as analog transfer characteristics of the hipdar transistors used in the device.

To analyze bridging faults of this class, consider a continuational block with inputs A 1 ....  $A_n$  and cutputs Z 1 ....  $Z_m$ . Consider that input A 1 is bridged with output Z 1 through a sufficient bridging resistance (R - X). Assuing that an input vector is applied under which there is a sensitized path from  $A_1$  to  $Z_1$  through an odd number of inversions. When A 1 is logic level '1', Z 1 is '0' without feedback bridging. The situation will be different in the presence of feedback bridging. Considering the case when rise and fall times are much smaller compared to propagation delay, then the output logic level (Z 1) changes after the propagation delay. In the above situation, oxillations will occur where the propagation delay determines the dock period of oxillations.

On the catary when the propagation delay is smaller than the rise or fall times, the catput will start changing before the input has time to stabilize. This leads to a situation where a rising or falling input signal starts influencing itself in the opposite direction before it reaches the switching threshold. This behavior needs to be analyzed using dynamic analysis taking into account the transistor characteristics, note capacitances etc., as static analysis alone will not suffice.

The two cases are illustrated in D-BJT BiCMOS gates with a feedark bridging fault using SPICE similation for an odd number of inverter dain (3 inverters) as shown in Figure 9. When the propagation delay was small, for example, one D-BJT BiCMOS gate, oscillations and not occur and the voltage level stabilized at an intermediate level (undefined). Effects of bridging resistance under feedback bridging conditions were studied. For low-bridging resistances, the voltage level stabilized at intermediate level. However, as the value of bridging resistance was increased, the effect of bridging became insignificant, resulting in correct logic levels.

When propagation delay is sufficiently large (with 3 or more inversions of D-BJT BioMOS stages),

oscillations occur. When the bridging resistance (R(x) is sufficiently small, the oscillations will touch either '0' or '1'. When propagation delay is just sufficiently large enough for oscillations, it will cause signals to cross the threshold voltage, and the requirement for oxillation [15] to occur is observed to be as given below

$$t_{pd} > \frac{t_r + t_f}{2}$$

Where t  $_{pd}$  is the propagation delay, t  $_{r}$  is the rise time and t

$_f$  is the fall-time

Example: SPICE similation using aspecific set of parameters for a chain of D-BJT BiCMOS NAND

gates exhibited the following characteristics: t $_{pd}/\text{gate} = 0.50 \text{ nSecs}, t$   $_{r} = 1.2 \text{ nSecs}, t$   $_{f} = 1.2 \text{ nSecs}.$  The above characteristics suggest that oxillations wild occur with a proportion delay of 1.5 nSecs for the device chain. Similations do not exhibit oscillations with one device (tpd = 0.5nSecs) but oscillations do occur with a device chain of 3 (t pd = 15 nSecs), as shown in Figure 10.

#### Conclusions 6

Effects of bidging failts in BiCMOS devices were examed. Range of resistance values affecting the logic levels in BiCMOS under bridging of logical nodes without feedback was presented along with their effects an noise immity. Powr suply current (IDDQ) monitoring for detection of bridging faults was shown Feedback bridging faults resulting in oscillations was presented.

#### References

- [1] A. R. Alvarez, BiCMOS Technology and Applications, Kluwer Academic Publishers, 1989.

- [2] R. Haken 'Process technology for submicron BiCMOS VLSI', IEEE Irtl. Sym on Graits and Systems, pp. 1971-1974, 1990.

- [3] B. C de, 'Is BiCMOS the next technology driver?', Electroics, pp 55-57, Feb 1988.

- [4] T. E. Magr, 'Sources of failures and yield improvement for VLSI and restructurable interconnects for RVLSI and WSI: Part I-Sources of failures and yield improvement for VLSI', Proc. IEEE, Vd. 72, pp 690-708, June 1984.

- [5] J. A. Abahamard W. K. Fuds, 'Fault and error models for VLSI', Proc. IEEE, Vd. 74, pp. 639-653, May 1986.

- [6] J. Gallay Y. Gozet and M. Vergiadt, 'Physical versus logical fault models in MOS LSI circuits: Impact on the testability', IEEE Trans. Compters, Vol. 629, pp 527-531. June 1980.

- [7] Y. K. Malaiya, B. Gupta, A. P. Jayasuma, R. Rajsuma, S. M. Meron and S. Yang 'Functional Fault modeling for elementary static storage elements', Technical report, Dept. of Corputer Science, Glorado State University April, 1989.

- [8] CCBeh, K. H. Arya, CE. Rake and K. E. Torku, 'Do stuck fault models reflect manufacturing defects?', Proc. IEEE Test Cof., pp. 35-42, Nov. 1982.

- [9] M. E. Levitt, K. Roy and J. A. Abraham 'BiCMOS fault models: Is stuck- at adequate?', Proc. ICD., pp. 294-297, Sep. 1990.

- [10] F. J. Fergsonard J. P. Slen, 'Extraction and Simulation of Realistic CMOS Faults using Inductive Fault Analysis', Proc. IEEE Int. Test Coff., pp 475-484, 1988.

- [11] J. P. Slen, W. Maly and F. J. Fergson, 'Inductive Fault Analysis of nMOS and CMOS Integrated Circuits', Research Report No. CMUCAS-85-51, Dept. of Electrical and Corputer Engineering Carregie-Mellon University, August 1985.

- [12] P. Lamureux and V. K. Agrawi, 'On-Stuck at Fault detection in nMOS circuits by Region Analysis', Proc. Infl. Test 6ff., pp 129-137, October 1983.

- [13] B. Gartos, Failure mechanisms, 'Fault hypothesis and Analytical Testing on LSI nMOS(HMOS) Circuits', VLSI '81, Univ. of Edubral, Academic Press, Augst 1981.

- [44] R. L. Wadsak, 'Fault Modeling and Logic Simulation of CMOS Integrated circuits', Bell Systems Technical Journal, May-Jure 1978, pp. 1449-1474.

- [15] Y. K. Malaiya, A. P. Jayasuma and R. Rajsum, 'A Detailed Examination of Bridging Faults', Proc. IEEE 6ff. on Capter Design, pp. 78-81, 1986.

- [16] R. Rajsuan, Y. K. Malaiya and A. P. Jayasuana, 'On Accuracy of Switch- Level Modeling of Bridging Faults in Complex Gates', Proc. IEEE Design Automation Conf., pp. 244-250, 1987.

- [17] S. M. Menn, A. P. Jayasuma and Y. K. Malaiya, 'Fault Modeling of ECL devices', Electronics Letters, pp 1105-1108, July 1990.

- [18] S. M. Meron, Y. K. Malaiya and A. P. Jayasuman, 'Fault Modeling and Testable Design of 2- level Complex ECL Gates', Proc. 4th SI/IEEE Intl. Sym on VLSI Design pp. 23-28, Jan. 1991.

- [19] D. A. Hodgs and H. G. Jackson, Analysis and Design of Digital Integrated Circuits, McGrawHill, 61, 3, 1983.

- [20] R. L. Geiger, P. E. Allenard N. R. Strader, VLSI Design Techniques for Analog and Digital Integrated Circuits, McGrawHill, @ 7, 1990.

- [21] S. M. Menn, 'Modeling, Analysis and Design for Testability of Bipolar/MOS VLSI', PhD. Dissertation, Dept. of Electrical Engineering Clorab State University (in peparation).

- [22] Fujitsu ECL & BiCMOS ASIC Selector Guide, pp 20-21, 1990

- [23] P. Banerjee and J. A. Abraham, "Generating Tests for Physical Failures in MOS Logic Circuits", Proc. Intl. Test Cof., pp 554-559, Oct. 1983.

- [24] Y. K. Mdaiya, 'Testing Stuck- On Faults in CMOS Integrated Circuits', Proc. IEEE Intl. 6df. on Capter-Aided Design pp 248-250, Nov. 1984.

- [25] C Tinar, M. Bueller, T. Grisweld, C Pina, F. Stott and L. Hess, 'Logical models of physical failures', Proc. IEEE Intl. Test Caf., pp 546-553, Nov. 1983.

- [26] J. Hlavica and E. Kotteck, 'Fault Model for TTL Circuits', Digital Processes, Vd. 2, pp 169-180, 1976.

- [27] S. M. Meron, A. P. Jayasuman and Y. K. Malaiya, 'On Bridging Faults in ECL Circuits', Proc. 5th Intl. 6af. on VLSI Design, pp 55-60, Jan 1992.

- [28] S. Xu and S. Y. H. Su, 'Testing Feedback Bridging Faults among Internal Input and Output Lines by Two Patterns', Proc. Ird. Caf. on Graits and Capters, pp 214-217, Sep 1982.