Instruction Set Architecture

Instruction Set Architecture

IsA = All of the programmer-visible components and operations of the computer

memory organization

address space -- how may locations can be addressed?

addressibility -- how many bits per location?

register set

how many? what size? how are they used?

instruction set

opcodes

data types

addressing modes

IsA provides all information needed for someone that wants to write a program in machine language

or translate from a high-level language to machine language.

LC-3 Overview: Memory and Registers

Memory

address space: 2¹6 locations (16-bit addresses)

addressability: 16 bits

Registers

temporary storage, accessed in a single machine cycle

accessing memory takes longer than a single cycle

eight general-purpose registers: R0 - R7

each 16 bits wide

how many bits to uniquely identify a register?

other registers

not directly addressable, but used by (and affected by) instructions

PC (program counter), condition codes

### LC-3 Overview: Instruction Set Opcodes 15 opcodes, 3 types of instructions Operate: ADD, AND, NOT Data movement: LD, LDI, LDR, LEA, ST, STR, STI Control: BR, JSR/JSRR, JMP, RTI, TRAP some opcodes set/clear condition codes, based on result: N = negative, Z = zero, P = positive (> 0) Data Types 16-bit 2's complement integer Addressing Modes

How is the location of an operand specified?

non-memory addresses: immediate, register

memory addresses: PC-relative, indirect, base+offset

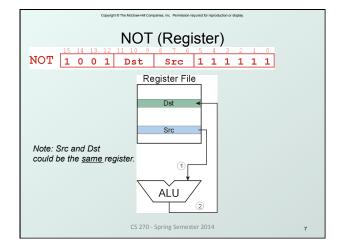

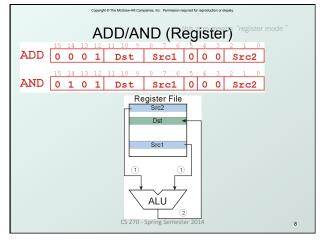

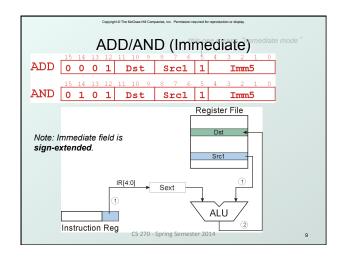

### Operate Instructions

- Only three operations: ADD, AND, NOT

- Source and destination operands are registers

- These instructions <u>do not</u> reference memory.

- ADD and AND can use "immediate" mode, where one operand is hard-wired into the instruction.

- Will show dataflow diagram with each instruction.

- illustrates <u>when</u> and <u>where</u> data moves to accomplish the desired operation

CS 270 - Spring Semester 2014

5 CS 270 - Spring S

## ● With only ADD, AND, NOT... • How do we subtract? • How do we OR? • How do we copy from one register to another? • How do we initialize a register to zero?

CS 270 - Spring Semester 2014

### Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display.

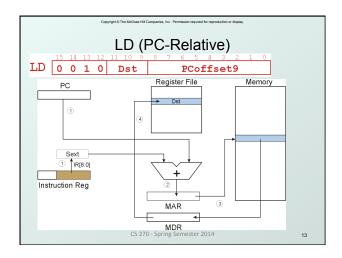

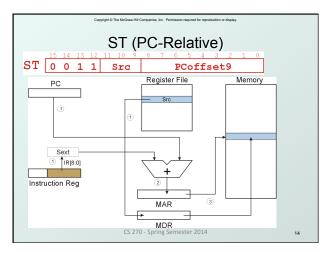

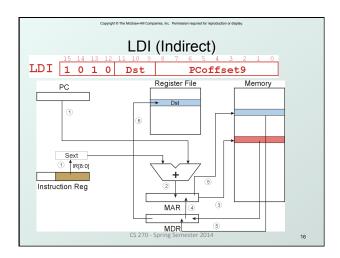

### **Data Movement Instructions**

- Load -- read data from memory to register

- LD: PC-relative mode

- LDR: base+offset mode

- LDI: indirect mode

- Store -- write data from register to memory

- ST: PC-relative mode

- STR: base+offset mode

- STI: indirect mode

- Load effective address -- compute address, save in register

- LEA: immediate mode

- does not access memory

CS 270 - Spring Semester 2014

### Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or displa

### PC-Relative Addressing Mode

- Want to specify address directly in the instruction

- But an address is 16 bits, and so is an instruction!

- After subtracting 4 bits for opcode and 3 bits for register, we have 9 bits available for address.

- Solution:

- Use the 9 bits as a <u>signed offset</u> from the current PC.

- 9 bits: -256 ≤ offset ≤ +255

- Can form address such that: PC 256 ≤ X ≤ PC +255

- Remember that PC is incremented as part of the FETCH phase;

- This is done <u>before</u> the EVALUATE ADDRESS stage.

CS 270 - Spring Semester 2014

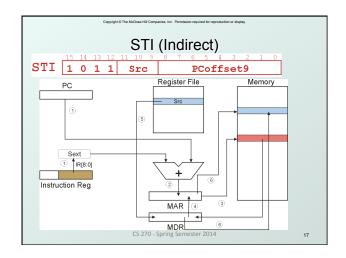

### Indirect Addressing Mode

- With PC-relative mode, can only address data within 256 words of the instruction.

- What about the rest of memory?

- Solution #1:

- Read address from memory location, then load/store to that address.

- First address is generated from PC and IR (just like PC-relative addressing), then content of that address is used as target for load/store.

CS 270 - Spring Semester 2014

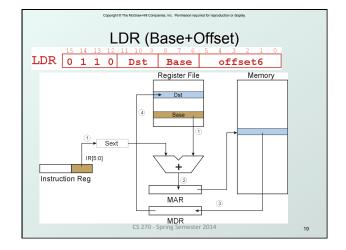

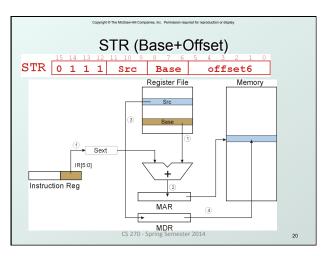

### Base + Offset Addressing Mode

- With PC-relative mode, can only address data within 256 words of the instruction.

- What about the rest of memory?

- Solution #2:

- Use a register to generate a full 16-bit address.

- 4 bits for opcode, 3 for src/dest register,

3 bits for base register -- remaining 6 bits are used as a signed offset.

- Offset is sign-extended before adding to base register.

CS 270 - Spring Semester 2014

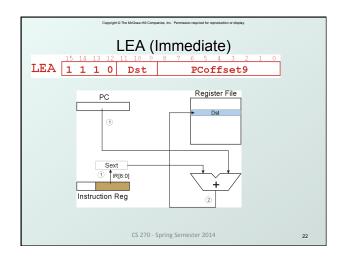

### Load Effective Address

Computes address like PC-relative (PC plus signed offset) and stores the result into a register.

**Note**: The <u>address</u> is stored in the register, not the contents of the memory location.

CS 270 - Spring Semester 2014

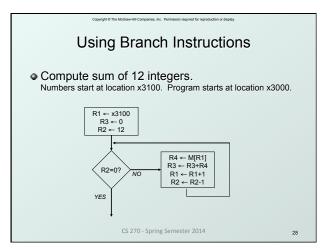

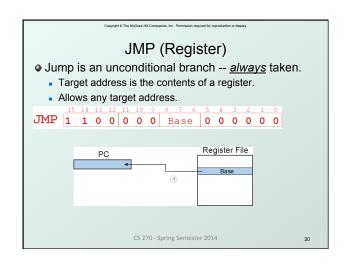

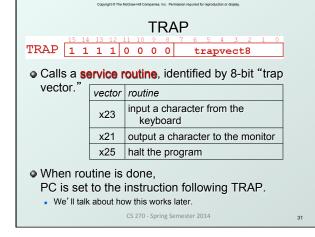

# Control Instructions Used to alter the sequence of instructions (by changing the Program Counter) Conditional Branch branch is taken if a specified condition is true signed offset is added to PC to yield new PC else, the branch is not taken PC is not changed, points to the next instruction Unconditional Branch (or Jump) always changes the PC TRAP changes PC to the address of an OS "service routine" routine will return control to the next instruction (after the TRAP)

### **Condition Codes**

- LC-3 has three condition code registers:

- N -- negative

- Z -- zero

- P -- positive (greater than zero)

- Set by any instruction that writes a value to a register

(ADD, AND, NOT, LD, LDR, LDI, LEA)

- Exactly one will be set at all times

- Based on the last instruction that altered a register

CS 270 - Spring Semester 2014

25

### Branch Instruction

- Branch specifies one or more condition codes.

- If the set bit is specified, the branch is taken.

- PC-relative addressing: target address is made by adding signed offset (IR[8:0]) to current PC.

- Note: PC has already been incremented by FETCH stage.

- Note: Target must be within 256 words of BR instruction.

- If the branch is not taken, the next sequential instruction is executed.

CS 270 - Spring Semester 2014

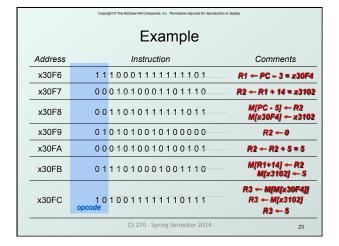

|                | Cop | syright © The McGraw-Hill Companies, Inc. Permission required for reproduc | tion or display.          |  |

|----------------|-----|----------------------------------------------------------------------------|---------------------------|--|

| Sample Program |     |                                                                            |                           |  |

| Address        |     | Instruction                                                                | Comments                  |  |

| x3000          | 1 1 | 10001011111111                                                             | R1 ← x3100 (PC+0xFF)      |  |

| x3001          | 0 1 | 01011011100000                                                             | R3 ← 0                    |  |

| x3002          | 0 1 | 01010010100000                                                             | R2 ← 0                    |  |

| x3003          | 0 0 | 01010010101100                                                             | R2 ← 12                   |  |

| x3004          | 0 0 | 00010000000101                                                             | If Z, goto x300A (PC+5)   |  |

| x3005          | 0 1 | 10100001000000                                                             | Load next value to R4     |  |

| x3006          | 0 0 | 01011011000001                                                             | Add to R3                 |  |

| x3007          | 0 0 | 01001001100001                                                             | Increment R1 (pointer)    |  |

| X3008          | 0 0 | 01010010111111                                                             | Decrement R2<br>(counter) |  |

| x3009          | 0 0 | 00111111111010                                                             | Goto x3004 (PC-6)         |  |

|                |     | CS 270 - Spring Semester 2014                                              | 29                        |  |

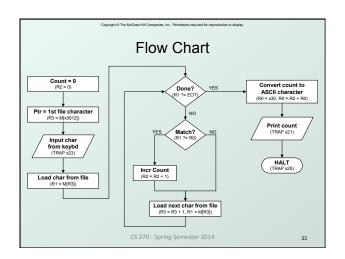

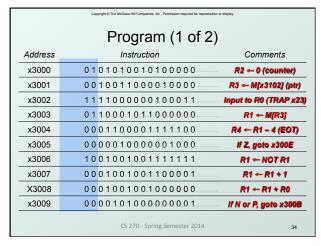

Another Example

Count the occurrences of a character in a file

Program begins at location x3000

Read character from keyboard

Load each character from a "file"

File is a sequence of memory locations

Starting address of file is stored in the memory location immediately after the program

If file character equals input character, increment counter

End of file is indicated by an ASCII value: EOT (x04)

At the end, print the number of characters and halt (assume there will be less than 10 occurrences of the character)

A special character used to indicate the end of a sequence is often called a sentinel.

Useful when you don't know ahead of time how many times to execute a loop.

|                  | Сор                      | sylight © The McGraw-Hill Companies, Inc. Permission required for reproductive | on or display.      |  |  |

|------------------|--------------------------|--------------------------------------------------------------------------------|---------------------|--|--|

| Program (2 of 2) |                          |                                                                                |                     |  |  |

| Address          |                          | Instruction                                                                    | Comments            |  |  |

| x300A            | 0 0                      | 01010010100001                                                                 | R2 ← R2 + 1         |  |  |

| x300B            | 0 0                      | 01011011100001                                                                 | R3 ← R3 + 1         |  |  |

| x300C            | 0 1                      | 10001011000000                                                                 | R1 ← M[R3]          |  |  |

| x300D            | 0 0                      | 00111111110110                                                                 | Goto x3004          |  |  |

| x300E            | 0 0                      | 10000000000100                                                                 | R0 ← M[x3013]       |  |  |

| x300F            | 0 0                      | 01000000000010                                                                 | R0 ← R0 + R2        |  |  |

| x3010            | 11                       | 11000000100001                                                                 | Print R0 (TRAP x21) |  |  |

| x3011            | 11                       | 11000000100101                                                                 | HALT (TRAP x25)     |  |  |

| X3012            | Starting Address of File |                                                                                |                     |  |  |

| x3013            | 0 0                      | 00000000110000                                                                 | ASCII x30 ( '0')    |  |  |

|                  |                          | CS 270 - Spring Semester 2014                                                  | 35                  |  |  |

### Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or disp

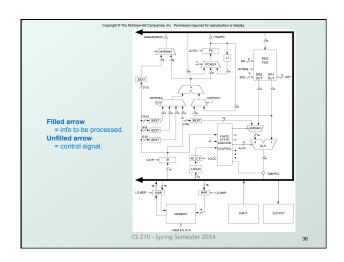

### **Data Path Components**

### Global bus

- special set of wires that carry a 16-bit signal to many components

- inputs to the bus are "tri-state devices", that only place a signal on the bus when they are enabled

- only one (16-bit) signal should be enabled at any time

control unit decides which signal "drives" the bus

- any number of components can read the bus

- register only captures bus data if it is write-enabled by the control unit

### Memory

- Control and data registers for memory and I/O devices

- memory: MAR, MDR (also control signal for read/write)

CS 270 - Spring Semester 2014

27

### \_ . \_ .. \_ .

### **Data Path Components**

### ALU

- Accepts inputs from register file and from sign-extended bits from IR (immediate field).

- Output goes to bus.

- used by condition code logic, register file, memory

### Register File

- Two read addresses (SR1, SR2), one write address (DR)

- Input from bus

- result of ALU operation or memory read

- Two 16-bit outputs

- used by ALU, PC, memory address

- data for store instructions passes through ALU

S 270 - Spring Semester 2014

### Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or displication

### **Data Path Components**

### PC and PCMUX

- Three inputs to PC, controlled by PCMUX

- 1.PC+1 FETCH stage

- 2.Address adder BR, JMP

- 3.bus TRAP (discussed later)

### ➤ MAR and MARMUX

- · Two inputs to MAR, controlled by MARMUX

- 1.Address adder LD/ST, LDR/STR

- 2.Zero-extended IR[7:0] -- TRAP (discussed later)

CS 270 - Spring Semester 2014

39

### Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display

### **Data Path Components**

### Condition Code Logic

- Looks at value on bus and generates N, Z, P signals

- Registers set only when control unit enables them (LD.CC)

- only certain instructions set the codes (ADD, AND, NOT, LD, LDI, LDR, LEA)

### Control Unit – Finite State Machine

- On each machine cycle, changes control signals for next phase of instruction processing

- who drives the bus? (GatePC, GateALU, ...)

- which registers are write enabled? (LD.IR, LD.REG, ...)

- which operation should ALU perform? (ALUK)

- Logic includes decoder for opcode, etc.

CS 270 - Spring Semester 2014