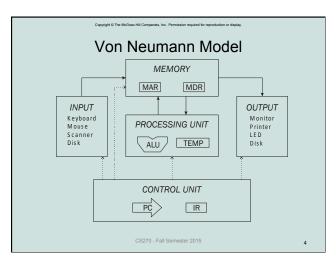

Interface to Memory

How does CPU get data to/from memory?

MAR: Memory Address Register

MDR: Memory Data Register

To DAD a location (A):

Write the address (A) into the MAR.

Send a "read" signal to the memory.

Read the data from MDR.

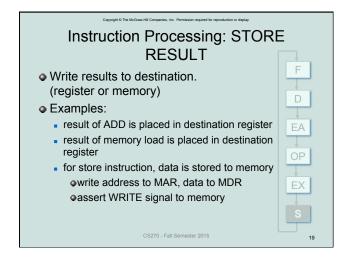

To STORE a value (X) to a location (A):

Write the data (X) to the MDR.

Write the address (A) into the MAR.

Send a "write" signal to the memory.

CS270 - Fall Semester 2015

# **Processing Unit**

# Functional Units

- ALU = Arithmetic and Logic Unit

- could have many functional units. (multiply, square root, ...)

- LC-3 performs ADD, AND, NOT

## Registers

- Small, temporary storage

- Operands and results of functional units

- LC-3 has eight registers (R0, ..., R7), each 16 bits wide

### Word Size

- number of bits processed by ALU in one instruction

- also width of registers

- LC-3 is 16 bits

CS270 - Fall Semester 2015

# Input and Output

- Devices for getting data into and out of computer memory

- Each device has its own interface, usually a set of registers like the memory's MAR and MDR

INPUT

Keyboard

Mouse

Scanner

Disk

OUTPUT Monitor Printer LED Disk

- LC-3 supports keyboard (input) and monitor (output)

- keyboard: data (KBDR) and status (KBSR) registers

- monitor: data register (DDR) and status register (DSR)

- Some devices provide both input and output

- disk, network

- Program that controls access to a device is usually called a driver.

CS270 - Fall Semester 2015

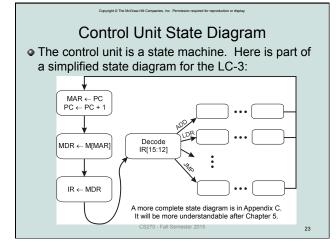

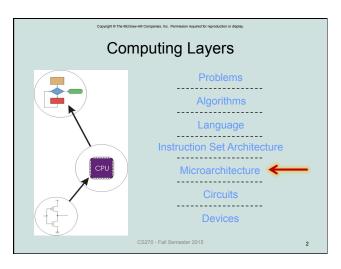

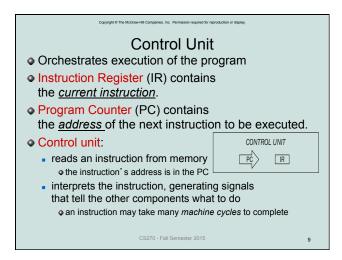

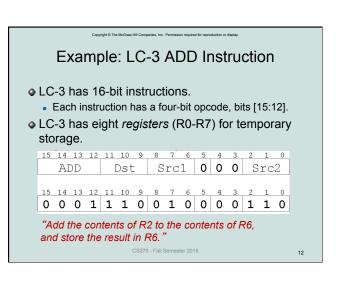

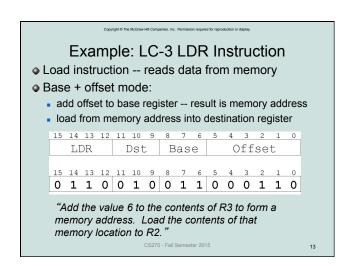

# Instruction The instruction is the fundamental unit of work: opcode: operation to be performed operands: data/locations to be used for operation An instruction is encoded as a sequence of bits. (Just like data!) Often, but not always, instructions have a fixed length, such as 16 or 32 bits. Control unit interprets instruction: generates sequence of control signals to carry out operation. Operation is either executed completely, or not at all. A computer's instructions and their formats is known as its Instruction Set Architecture (ISA).

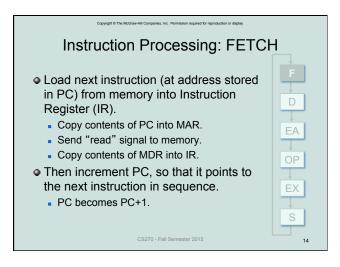

Changing the Sequence of Instructions

In the FETCH phase,

we increment the Program Counter by 1.

What if we don't want to always execute the

instruction

that follows this one?

examples: loop, if-then, function call

Need special instructions that change the contents

of the PC.

These are called *control instructions*.

jumps are unconditional -- they always change the PC

branches are conditional -- they change the PC only if

some condition is true (e.g., the result of an ADD is

zero)

CS270 - Fall Semester 2015

# Example: LC-3 JMP Instruction

Set the PC to the value contained in a register.

This becomes the address of the next instruction to fetch.

| 15  | 5   | 14 | 13  | 12 | 11 | 10 | 9 | 8    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|-----|----|-----|----|----|----|---|------|---|---|---|---|---|---|---|---|

|     | JMP |    |     |    | 0  | 0  | 0 | Base |   |   | 0 | 0 | 0 | 0 | 0 | 0 |

| 1.5 | 5   | 14 | 1.3 | 12 | 11 | 10 | 9 | 8    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|     |     |    |     |    |    |    |   | 0    |   |   |   |   |   |   |   |   |

"Load the contents of R3 into the PC."

CS270 - Fall Semester 2015

# **Instruction Processing Summary**

- Instructions look just like data -- it's all interpretation.

- Three basic kinds of instructions:

- computational instructions (ADD, AND, ...)

- data movement instructions (LD, ST, ...)

- control instructions (JMP, BRnz, ...)

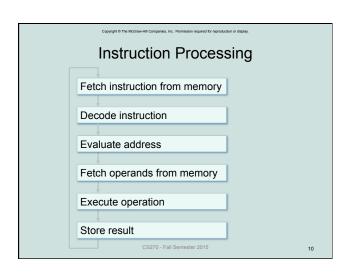

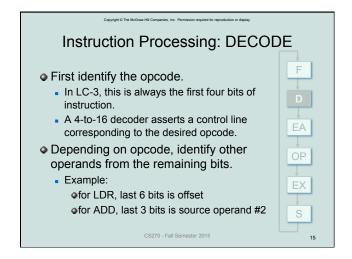

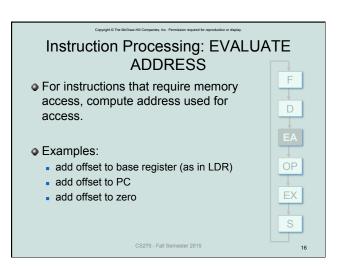

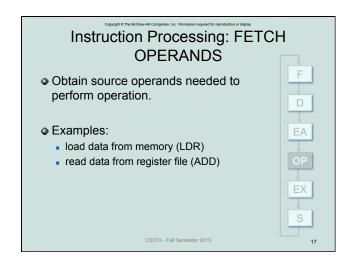

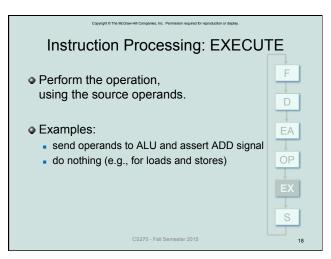

- Six basic phases of instruction processing:

$$F \rightarrow D \rightarrow EA \rightarrow OP \rightarrow EX \rightarrow S$$

- not all phases are needed by every instruction

- phases may take variable number of machine cycles

CS270 - Fall Semester 2015

22