I/O: Connecting to Outside World

So far, we've learned how to:

compute with values in registers

load data from memory to registers

store data from registers to memory

But where does data in memory come from?

And how does data get out of the system so that humans can use it?

I/O: Connecting to the Outside World

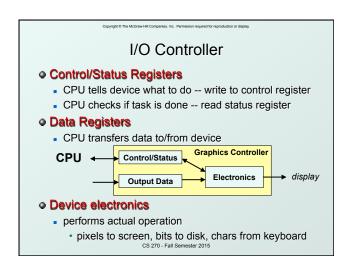

Types of I/O devices characterized by:

behavior: input, output, storage

input: keyboard, motion detector, network interface

output: monitor, printer, network interface

storage: disk, CD-ROM

data rate: how fast can data be transferred?

keyboard: 100 bytes/sec

disk: 30 MB/s

network: 1 Mb/s - 1 Gb/s

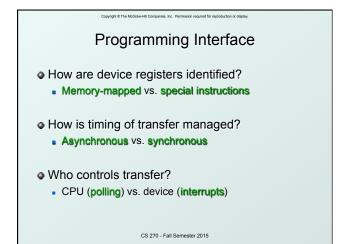

# Transfer Timing I/O events generally happen much slower than CPU cycles. Synchronous data supplied at a fixed, predictable rate CPU reads/writes every X cycles Asynchronous data rate less predictable CPU must synchronize with device, so that it doesn't miss data or write too quickly

CS 270 - Fall Semester 2015

# **Transfer Control**

• Who determines when the next data transfer occurs?

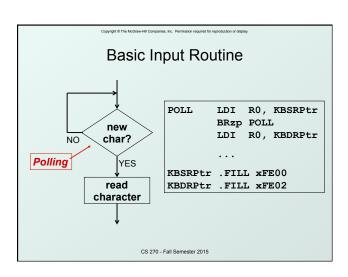

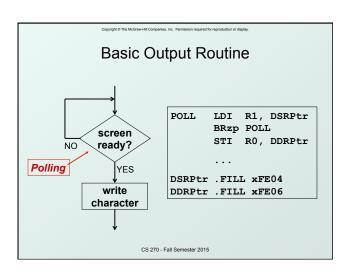

### Polling

- CPU keeps checking status register until <u>new data</u> arrives OR <u>device ready</u> for next data

- "Are we there yet? Are we there yet? Are we ...

### Interrupts

- Device sends a special signal to CPU when <u>new data</u> arrives OR <u>device ready</u> for next data

- CPU can be performing other tasks instead of polling device

- "Wake me when we get there."

CS 270 - Fall Semester 2015

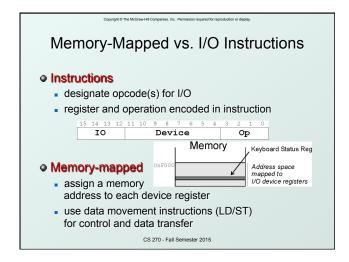

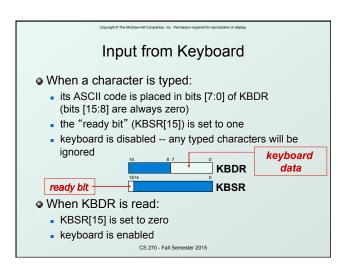

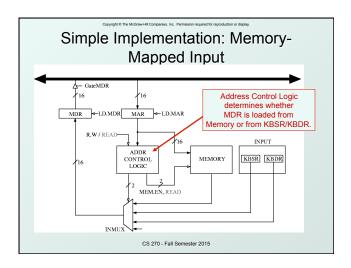

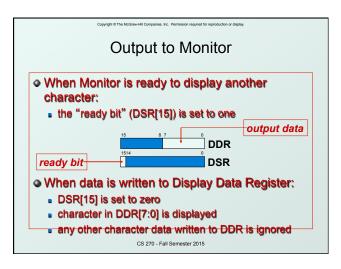

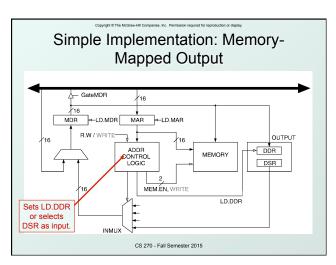

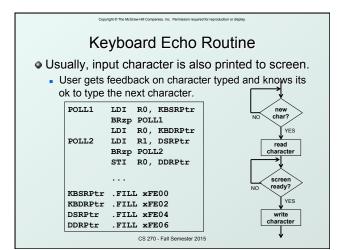

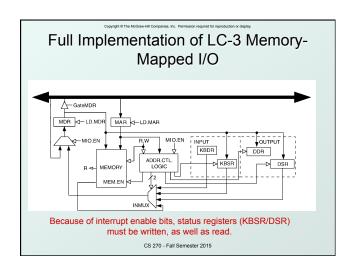

### LC-3 Location I/O Register Function **Keyboard Status** Bit [15] is one when keyboard has xFE00 (KBSR) Bits [7:0] contain the last character xFE02 Keyboard Data (KBDR) typed on keyboard. Bit [15] is one when device ready Display Status (DSR) xFE04 to display char on screen. Character written to bits [7:0] will xFE06 Display Data (DDR) be displayed on screen. Asynchronous devices synchronized through status registers Polling and Interrupts

Interrupt details will be discussed in Chapter 10

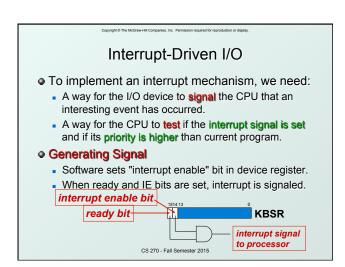

### Interrupt-Driven I/O

- External device can:

- (1) Force currently executing program to stop.

- (2) Have the processor satisfy the device needs.

- (3) Resume the program as if nothing happened.

- Why?

- Polling consumes a lot of cycles, especially for rare events – these cycles can be used for more computation.

- Example: Process previous input while collecting current input. (See Example 8.1 in text.)

CS 270 - Fall Semester 2015

## **Priority**

- Every instruction executes at a stated level of urgency.

- LC-3: 8 priority levels (PL0-PL7)

- Example:

- Payroll program runs at PL0.

- •Nuclear power correction program runs at PL6.

- It's OK for PL6 device to interrupt PL0 program, but not the other way around.

- Priority encoder selects highest-priority device, compares to current processor priority level, and generates interrupt signal if appropriate.

CS 270 - Fall Semester 2015

# Testing for Interrupt Signal CPU looks at signal between STORE and FETCH phases. If not set, continues with next instruction. If set, transfers control to interrupt service routine. More details in Chapter 10. CS 270 - Fall Semester 2015

# **Review Questions**

- What is the danger of not testing the DSR before writing data to the screen?

- What is the danger of not testing the KBSR before reading data from the keyboard?

- What if the Monitor were a synchronous device, e.g., we know that it will be ready 1 microsecond after character is written.

- Can we avoid polling? How?

- What are advantages and disadvantages?

CS 270 - Fall Semester 2015

### opyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or displi

### **Review Questions**

- Do you think polling is a good approach for other devices, such as a disk or a network interface?

- What is the advantage of using LDI/STI for accessing device registers?

CS 270 - Fall Semester 2015