## Midterm 2 Review Chapters 4-16 LC-3

You will be allowed to use the one page summary.

## **LC-3 Overview: Instruction Set**

#### **Opcodes**

- 15 opcodes

- Operate instructions: ADD, AND, NOT

- Data movement instructions: LD, LDI, LDR, LEA, ST, STR, STI

- Control instructions: BR, JSR/JSRR, JMP, RTI, TRAP

- some opcodes set/clear *condition codes*, based on result:

> N = negative, Z = zero, P = positive (> 0)

## Data Types

16-bit 2's complement integer

#### **Addressing Modes**

- How is the location of an operand specified?

- non-memory addresses: *immediate*, *register*

- memory addresses: PC-relative, indirect, base+offset

| ADD/AND (Immediate) this one means "immediate mode |    |    |    |    |         |   |    |   | e mode " |   |   |    |   |   |  |

|----------------------------------------------------|----|----|----|----|---------|---|----|---|----------|---|---|----|---|---|--|

|                                                    | 15 | 14 | 13 | 12 | 11 10 9 | 8 | 7  | 6 | 5        | 4 | 3 | 2  | 1 | 0 |  |

| ADD                                                | 0  | 0  | 0  | 1  | Dst     | S | rc | 1 | 1        |   | I | mm | 5 |   |  |

|                                                    |    |    |    |    | 11 10 9 |   |    |   |          |   |   | 2  | 1 | 0 |  |

| AND                                                | 0  | 1  | 0  | 1  | Dst     | S | rc | 1 | 1        |   | I | mm | 5 |   |  |

Assembly Ex: Add R3, R3, #1

*Note: Immediate field is sign-extended.*

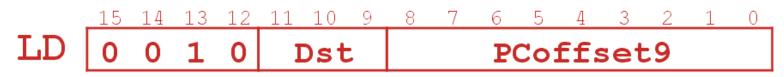

## Load and Store instructions

Example: LD R1, Label1 R1 is loaded from memory location labelled Label1

LDI 1010 Dst PCoffset9

Example: LDI R1, Label1 R1 is loaded from address found at location Label1

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

LDR

0

1

1

0

Dst

Base

offset6

0

Example: LDR R1, R4, #1 R1 is loaded from address pointed by R4 with offset 1. Store instructions use the same addressing modes, except the register contents are written to a memory location.

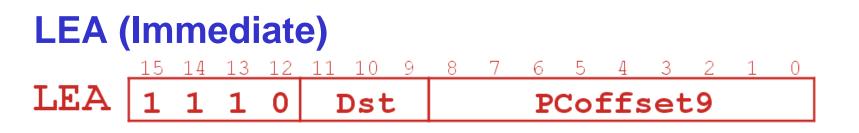

#### Assembly Ex: LEA R1, Lab1

Used to initialize a pointer.

## **Condition Codes**

LC-3 has three condition code registers:

- N -- negative

- Z -- zero

- **P** -- positive (greater than zero)

- Set by any instruction that writes a value to a register (ADD, AND, NOT, LD, LDR, LDI, LEA)

- Exactly one will be set at all times

- Based on the last instruction that altered a register

Assembly Ex: BRz, Label

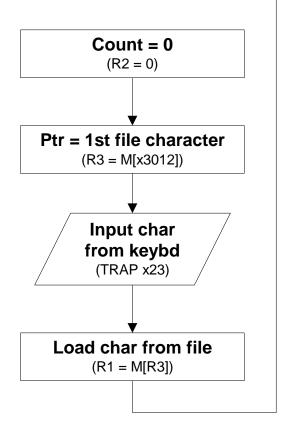

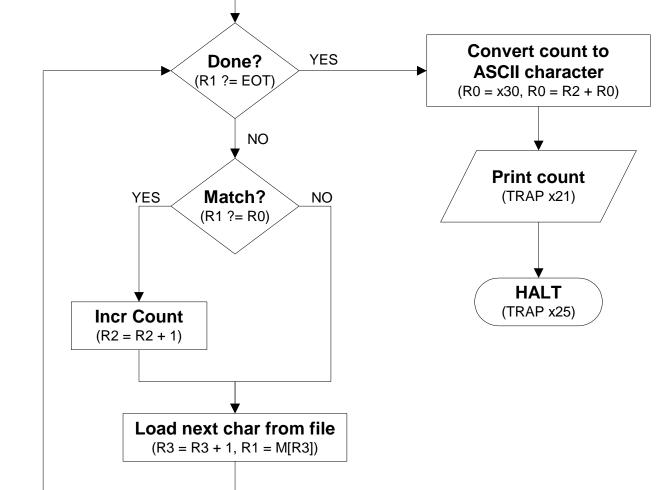

## **Count characters in a "file": Flow Chart**

|                        | .ORIG x3000                             |

|------------------------|-----------------------------------------|

|                        | AND R2, R2, #0 ; init counter           |

|                        | LD R3, PTR ; R3 pointer to chars        |

|                        | GETC ; R0 gets char input               |

|                        | LDR R1, R3, #0; R1 gets first char      |

| TEST                   | ADD R4, R1, #-4 ; Test for EOT          |

|                        | BRz OUTPUT ; done?                      |

| ;Test charact          | ter for match, if so increment count.   |

|                        | NOT R1, R1                              |

|                        | ADD R1, R1, R0 ; If match, R1 = xFFFF   |

|                        | NOT R1, R1 ; If match, R1 = x0000       |

|                        | BRnp GETCHAR ; No match, no increment   |

|                        | ADD R2, R2, #1                          |

| ; Get next ch          | aracter from file.                      |

| GETCHAR                | ADD R3, R3, #1 ; Point to next cha.     |

|                        | LDR R1, R3, #0 ; R1 gets next char      |

|                        | BRnzp TEST                              |

| ; Output the           | count.                                  |

| OUTPUT                 | LD R0, ASCII ; Load ASCII template      |

|                        | ADD R0, R0, R2 ; Covert binary to ASCII |

|                        | OUT ; ASCII code is displayed           |

| <b>0</b> , <b>1</b>    | HALT ; Halt machine                     |

| ; Storage for<br>ASCII | pointer and ASCII template<br>FILL      |

| PTR                    | .FILL                                   |

|                        | .END                                    |

x0030 x4000

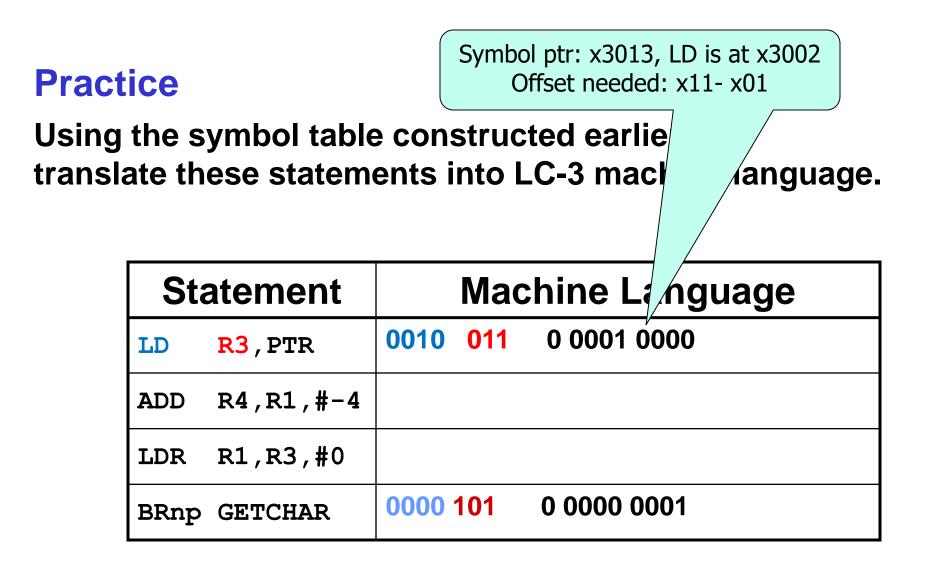

#### Count Characters Symbol Table: fill yourself

| Symbol  | Address |  |  |  |

|---------|---------|--|--|--|

| TEST    | x3004   |  |  |  |

| GETCHAR | x300B   |  |  |  |

| OUTPUT  |         |  |  |  |

| ASCII   |         |  |  |  |

| PTR     | x3013   |  |  |  |

## **Assembler Directives**

#### **Pseudo-operations**

- do not refer to operations executed by program

- used by assembler

- look like instruction, but "opcode" starts with dot

| Opcode    | Operand               | Meaning                                                                   |

|-----------|-----------------------|---------------------------------------------------------------------------|

| .ORIG     | address               | starting address of program                                               |

| . END     |                       | end of program                                                            |

| .BLKW     | n                     | allocate n words of storage                                               |

| .FILL     | n                     | allocate one word, initialize with value n                                |

| . STRINGZ | n-character<br>string | allocate n+1 locations,<br>initialize w/characters and null<br>terminator |

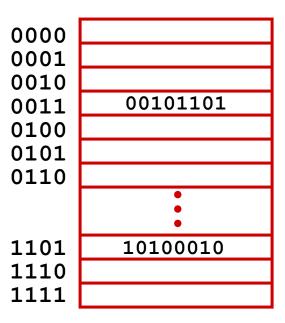

## Memory

## $2^k \ge m$ array of stored bits

#### Address

• unique (k-bit) identifier of location

#### Contents

• *m*-bit value stored in location

#### **Basic Operations:**

LOAD

read a value from a memory location

STORE

• write a value to a memory location

# TRAP Instruction 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 TRAP 1 1 1 0 0 0 0 trapvect8

#### **Trap vector**

- identifies which system call to invoke

- 8-bit index into table of service routine addresses

- > in LC-3, this table is stored in memory at 0x0000 0x00FF

- >8-bit trap vector is zero-extended into 16-bit memory address

#### Where to go

lookup starting address from table; place in PC

#### How to get back

• save address of next instruction (current PC) in R7

## **Trap Codes**

LC-3 assembler provides "pseudo-instructions" for each trap code, so you don't have to remember them.

| Code | Equivalent | Description                                                                                           |

|------|------------|-------------------------------------------------------------------------------------------------------|

| HALT | TRAP x25   | Halt execution and print message to console.                                                          |

| IN   | TRAP x23   | Print prompt on console,<br>read (and echo) one character from keybd.<br>Character stored in R0[7:0]. |

| OUT  | TRAP x21   | Write one character (in R0[7:0]) to console.                                                          |

| GETC | TRAP x20   | Read one character from keyboard.<br>Character stored in R0[7:0].                                     |

| PUTS | TRAP x22   | Write null-terminated string to console.<br>Address of string is in R0.                               |

### **Example: Using the TRAP Instruction**

.ORIG x3000

| LD R2, TERM    | ; Load negative ASCII '7' |

|----------------|---------------------------|

| LD R3, ASCII   | ; Load ASCII difference   |

| TRAP x23       | ; input character         |

| ADD R1, R2, R0 | ; Test for terminate      |

| BRZ EXIT       | ; Exit if done            |

| ADD R0, R0, R3 | ; Change to lowercase     |

| TRAP x21       | ; Output to monitor       |

| BRnzp AGAIN    | ; again and again         |

| .FILL xFFC9    | ; -'7'                    |

| .FILL x0020    | ; lowercase bit           |

| TRAP x25       | ; halt                    |

| . END          |                           |

AGAIN

TERM ASCII EXIT

#### **Example: Output Service Routine**

|                | .ORIG   | x043  | 30        | ; |  |

|----------------|---------|-------|-----------|---|--|

|                | ST      | R7,   | SaveR7    | ; |  |

|                | ST      | R1,   | SaveR1    |   |  |

| ; Writ         | te chai | racte | er        |   |  |

| TryWrite       | LDI     | R1,   | DSR       | ; |  |

|                | BRzp    | TryV  | Write     | ; |  |

| WriteIt        | STI     | R0,   | DDR       | ; |  |

| ; <b>Ret</b> u | ırn fra | om Tl | RAP       |   |  |

| Return         | LD      | R1,   | SaveR1    | ; |  |

|                | LD      | R7,   | SaveR7    |   |  |

|                | RET     |       |           | ; |  |

| DSR            | .FILL   | xF3I  | <b>TC</b> |   |  |

| DDR            | .FILL   | xF3I  | FF        |   |  |

| SaveR1         | .FILL   | 0     |           |   |  |

| SaveR7         | .FILL   | 0     |           |   |  |

|                | . END   |       |           |   |  |

save R7 & R1 get status look for bit 15 on write char restore R1 & R7 back to user stored in table, location x21

syscall address

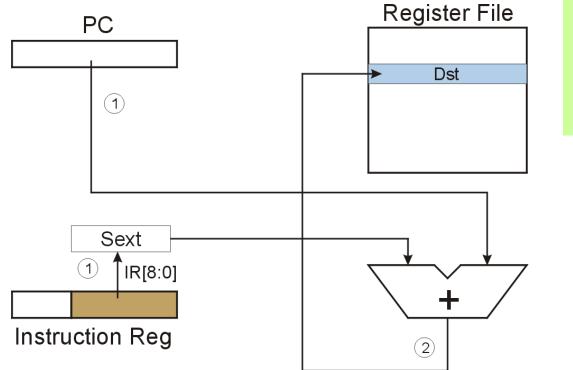

#### **JSR Instruction** 10 9 8 7 6 5 4 3 2 12 11 15 JSR 1

Jumps to a location (like a branch but unconditional), and saves current PC (addr of next instruction) in R7.

- saving the return address is called "linking"

- target address is PC-relative (PC + Sext(IR[10:0]))

- bit 11 specifies addressing mode

$\succ$  if =1, PC-relative: target address = PC + Sext(IR[10:0])

$\succ$  if =0, register: target address = contents of register IR[8:6]

PCoffset11

1

0

#### **Example: Negate the value in R0**

| 2sComp | NOT | R0, | R0  |    | ; | flip bits        |

|--------|-----|-----|-----|----|---|------------------|

|        | ADD | R0, | R0, | #1 | ; | add one          |

|        | RET |     |     |    | ; | return to caller |

#### To call from a program (within 1024 instructions):

; need to compute R4 = R1 - R3 ADD R0, R3, #0 ; copy R3 to R0 JSR 2sComp ; negate ADD R4, R1, R0 ; add to R1

Note: Caller should save R0 if we'll need it later!

## **RET (JMP R7)**

How do we transfer control back to instruction following the TRAP?

We saved old PC in R7.

- JMP R7 gets us back to the user program at the right spot.

- LC-3 assembly language lets us use RET (return) in place of "JMP R7".

Must make sure that service routine does not change R7, or we won't know where to return.

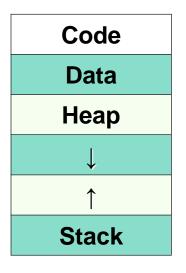

## Memory Usage

- Instructions are stored in code segment

- Global data is stored in data segment

- Local variables, including arryas, uses stack

- Dynamically allocated memory uses heap

- Code segment is write protected

- Initialized and uninitialized globals

- Stack size is usually limited

- Stack generally grows from higher to lower addresses.

## **Basic Push and Pop Code**

For our implementation, stack grows downward (when item added, TOS moves closer to 0)

#### Push R0

ADD R6, R6, #-1 ; decrement stack ptr STR R0, R6, #0 ; store data (R0)

#### Pop R0

LDR R0, R6, #0 ; load data from TOS ADD R6, R6, #1 ; decrement stack ptr

Sometimes a Pop only adjusts the SP.

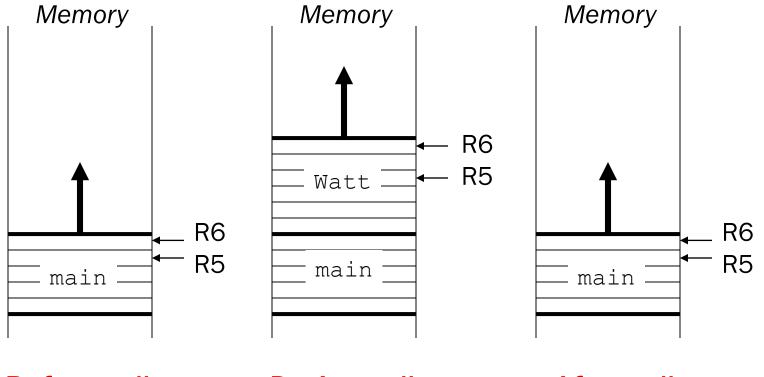

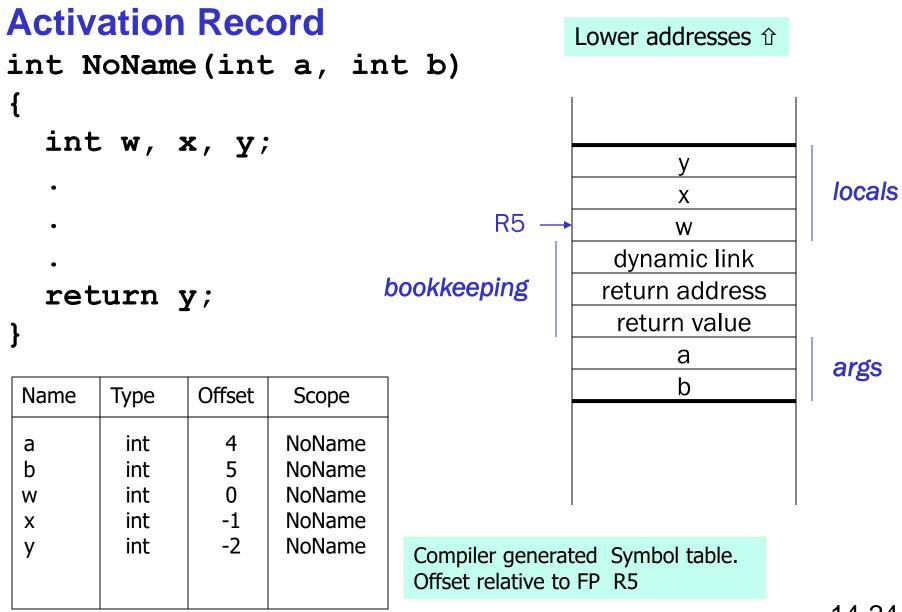

## **Run-Time Stack**

**Before call**

**During call**

After call

```

Example Function Call

int Volta(int q, int r)

{

int k;

int m;

return k;

}

int Watt(int a)

{

int w;

• • •

w = Volta(w, 10);

return w;

```

## **Summary of LC-3 Function Call Implementation**

- 1. Caller pushes arguments (last to first).

- 2. Caller invokes subroutine (JSR).

- **3.** Callee allocates return value, pushes R7 and R5.

- 4. Callee allocates space for local variables.

- **5.** Callee executes function code.

- 6. Callee stores result into return value slot.

- 7. Callee pops local vars, pops R5, pops R7.

- 8. Callee returns (JMP R7).

- 9. Caller loads return value and pops arguments.

- **10. Caller resumes computation...**

## **Example: LC-3 Code**

; i is 1st local (offset 0), ptr is 2nd (offset -1) ; i = 4;

|        | AND    | R0,   | R0, | #0          | ; clear R0                     |

|--------|--------|-------|-----|-------------|--------------------------------|

|        | ADD    | R0,   | R0, | #4          | ; put 4 in R0                  |

|        | STR    | R0,   | R5, | <b>#</b> 0  | ; store in i                   |

| ;ptr = | = &i   |       |     |             |                                |

|        | ADD    | R0,   | R5, | #0          | ; R0 = R5 + 0 (addr of i)      |

|        | STR    | R0,   | R5, | <b>#</b> -1 | ; store in ptr                 |

| ;*ptr  | = *pt: | r + 1 | ;   |             |                                |

|        | LDR    | R0,   | R5, | <b>#-1</b>  | ; R0 = ptr                     |

|        | LDR    | R1,   | R0, | #0          | ; load contents (*ptr)         |

|        | ADD    | R1,   | R1, | #1          | ; add one                      |

|        | STR    | R1,   | R0, | <b>#</b> 0  | ; store result where R0 points |

## Input/Output

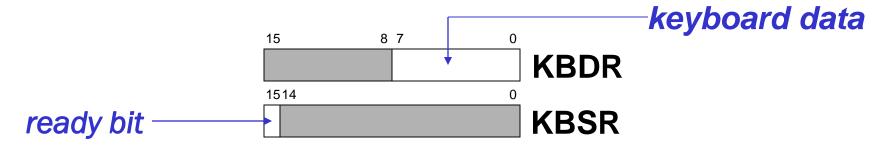

## Input from Keyboard

#### When a character is typed:

- its ASCII code is placed in bits [7:0] of KBDR (bits [15:8] are always zero)

- the "ready bit" (KBSR[15]) is set to one

- keyboard is disabled -- any typed characters will be ignored

#### When KBDR is read:

- KBSR[15] is set to zero

- keyboard is enabled

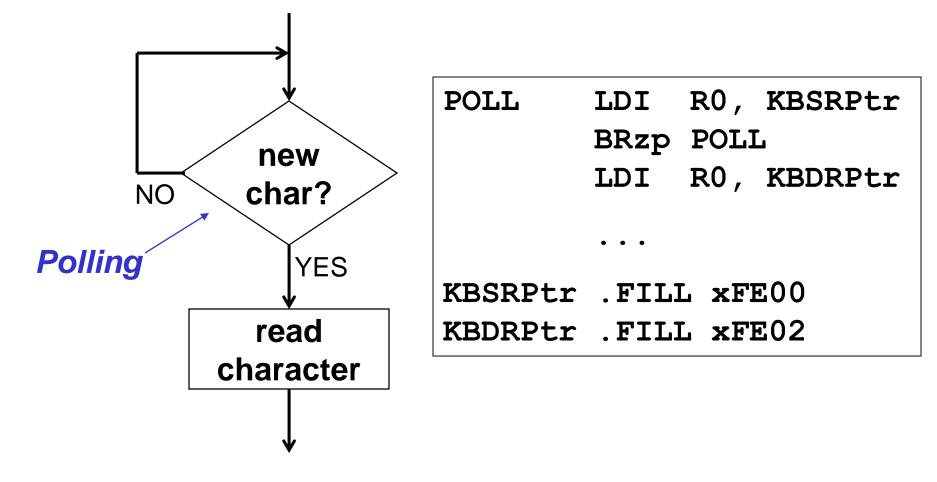

## **Basic Input Routine**

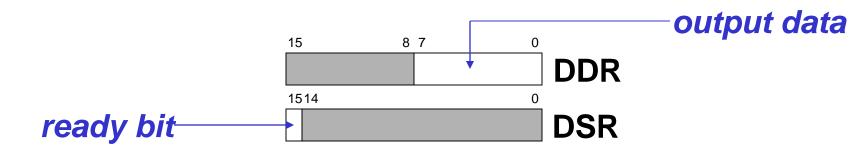

## **Output to Monitor**

#### When Monitor is ready to display another character:

• the "ready bit" (DSR[15]) is set to one

#### When data is written to Display Data Register:

- DSR[15] is set to zero

- character in DDR[7:0] is displayed

- any other character data written to DDR is ignored (while DSR[15] is zero)

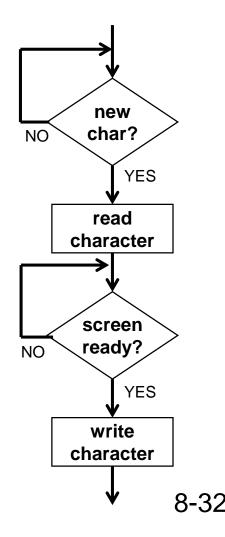

## **Keyboard Echo Routine**

#### Usually, input character is also printed to screen.

• User gets feedback on character typed and knows its ok to type the next character.

| LDI   | R0,                                                     | KBSRPtr                                    |

|-------|---------------------------------------------------------|--------------------------------------------|

| BRzp  | POL                                                     | ե1                                         |

| LDI   | R0,                                                     | KBDRPtr                                    |

| LDI   | R1,                                                     | DSRPtr                                     |

| BRzp  | POL                                                     | ե2                                         |

| STI   | R0,                                                     | DDRPtr                                     |

|       |                                                         |                                            |

| • • • |                                                         |                                            |

| .FIL  | L xFl                                                   | E00                                        |

| .FIL  | L xFl                                                   | E02                                        |

| .FIL  | L xFl                                                   | E04                                        |

| .FIL  | L xFl                                                   | E06                                        |

|       | BRzp<br>LDI<br>LDI<br>BRzp<br>STI<br><br>.FILI<br>.FILI | BRzp POL<br>LDI R0,<br>LDI R1,<br>BRzp POL |

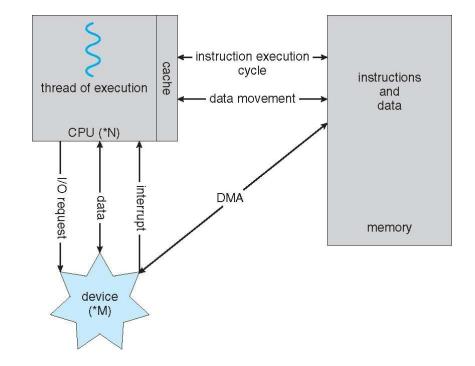

## **Interrupt-Driven I/O**

- **External device can:**

- (1) Force currently executing program to stop;

- (2) Have the processor satisfy the device's needs; and

- (3) Resume the stopped program as if nothing happened.

Interrupt is an unscripted subroutine call, triggered by an external event.

## **Interrupt-Driven I/O**

To implement an interrupt mechanism, we need:

- A way for the I/O device to signal the CPU that an interesting event has occurred.

- A way for the CPU to test whether the interrupt signal is set and whether its priority is higher than the current program.

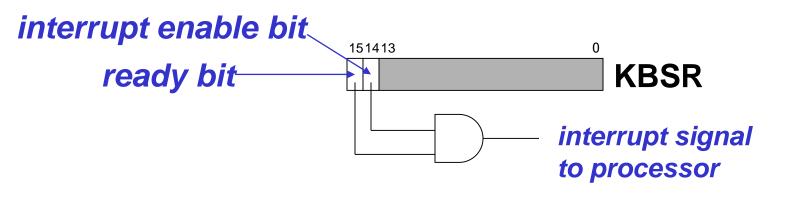

#### **Generating Signal**

- Software sets "interrupt enable" bit in device register.

- When ready bit is set and IE bit is set, interrupt is signaled.

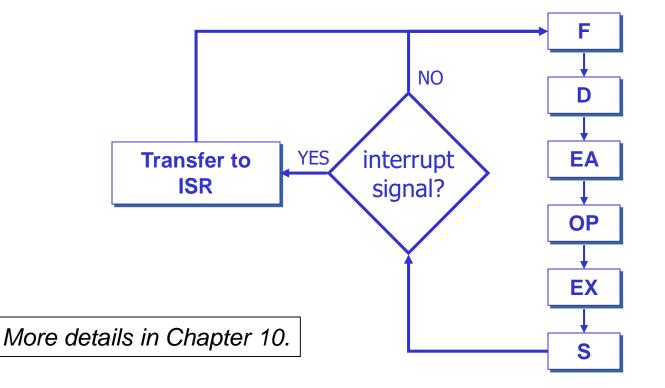

## **Testing for Interrupt Signal**

CPU looks at signal between STORE and FETCH phases. If not set, continues with next instruction.

If set, transfers control to interrupt service routine.

## **Processor State**

- Must be saved before servicing an interrupt.

- What state is needed to completely capture the state of a running process?

## Processor Status Register 15 14 13 12 10 9 8 7 6 5 4 3 2 1 0 P PL PL N Z P

#### LC-3: 8 priority levels (PL0-PL7)

## **Program Counter**

Pointer to next instruction to be executed.

#### Registers

All temporary state of the process that's not stored in memory.

## **Direct Memory Access Structure**

high-speed I/O devices Device controller transfers blocks of data from buffer storage directly to main memory without CPU intervention

Only one interrupt is generated per block