| Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display. |                           |

|----------------------------------------------------------------------------------------------|---------------------------|

| Instruction Set Architecture                                                                 | LC-3 (                    |

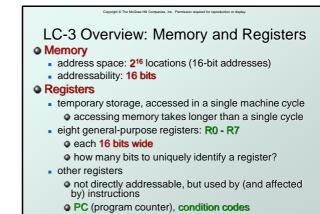

| ISA = All of the programmer-visible                                                          | Memory                    |

| components and operations of the computer                                                    | <ul> <li>addre</li> </ul> |

| memory organization                                                                          | <ul> <li>addre</li> </ul> |

| • address space how may locations can be addressed?                                          | Registe                   |

| addressibility how many bits per location?                                                   | tempo                     |

| <ul> <li>register set</li> <li>how many? what size? how are they used?</li> </ul>            | ac                        |

| <ul> <li>instruction set</li> </ul>                                                          | eight                     |

| opcodes                                                                                      | • ea                      |

| <ul> <li>data types</li> </ul>                                                               | • bo                      |

| <ul> <li>addressing modes</li> </ul>                                                         | • other                   |

| ISA provides all information needed for someone that                                         |                           |

| wants to write a program in machine language                                                 | • no                      |

| <ul> <li>or translate from a high-level language to machine language.</li> </ul>             | by)                       |

|                                                                                              | • P0                      |

| CS 270 - Fall Semester 2016 3                                                                |                           |

CS 270 - Fall Semester 2016

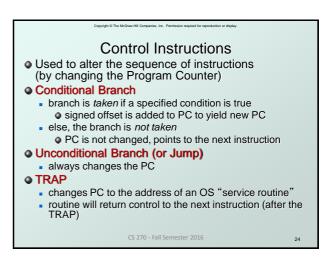

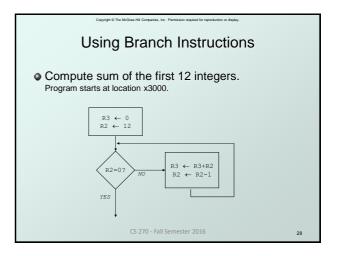

# LC-3 Overview: Instruction Set

# Opcodes

- 15 opcodes, 3 types of instructions

- Operate: ADD, AND, NOT

- Data movement: LD, LDI, LDR, LEA, ST, STR, STI

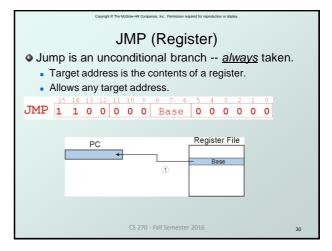

- Control: BR, JSR/JSRR, JMP, RTI, TRAP

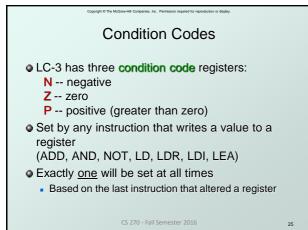

- some opcodes set/clear condition codes, based on result:

- $\bullet N$  = negative, Z = zero, P = positive (> 0)

- Data Types

- 16-bit 2's complement integer

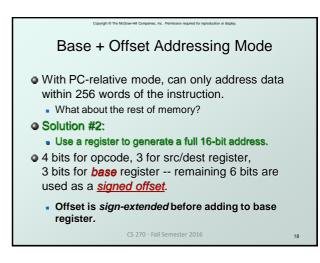

#### Addressing Modes

- How is the location of an operand specified?

- non-memory addresses: immediate, register

- memory addresses: PC-relative, indirect, base+offset

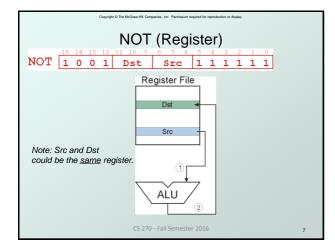

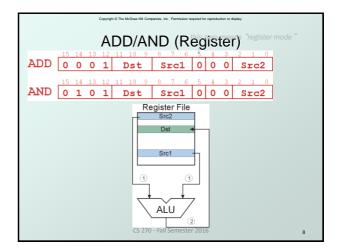

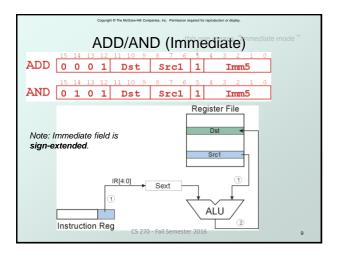

# Operate Instructions Only three operations: ADD, AND, NOT Source and destination operands are registers These instructions <u>do not</u> reference memory.

- ADD and AND can use "immediate" mode,

- where one operand is hard-wired into the instruction.

- Will show dataflow diagram with each instruction.

- illustrates <u>when</u> and <u>where</u> data moves to accomplish the desired operation

CS 270 - Fall Semester 2016

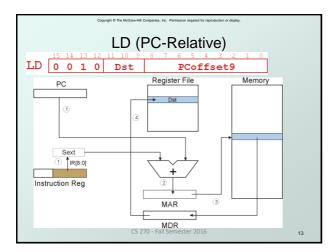

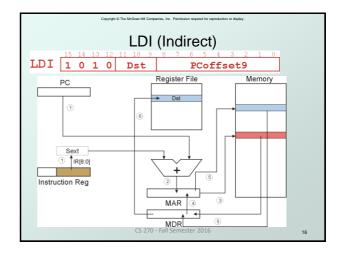

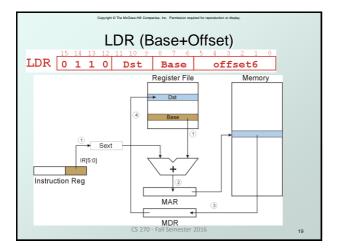

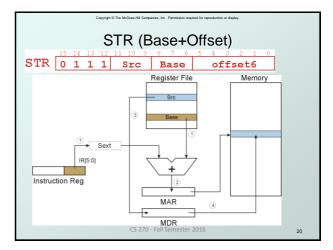

# **Data Movement Instructions** Load -- read data from memory to register LD: PC-relative mode LDR: base+offset mode LDI: indirect mode

wight © The McGraw Hill Companies Inc. Remission maximal for resenduction or depin

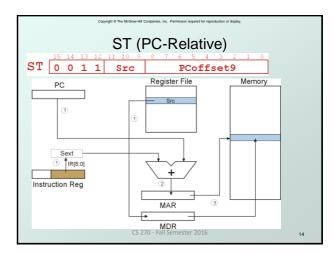

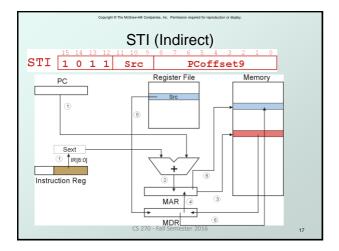

- Store -- write data from register to memory

- ST: PC-relative mode

- STR: base+offset mode

- STI: indirect mode

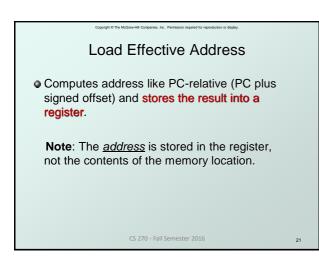

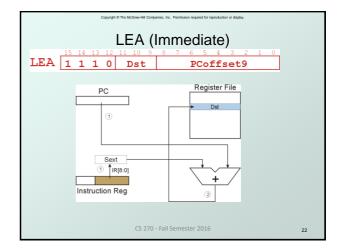

- Load effective address -- compute address, save in register

- LEA: immediate mode

- does not access memory

CS 270 - Fall Semester 2016

11

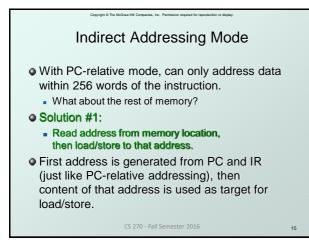

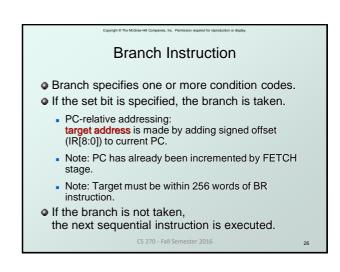

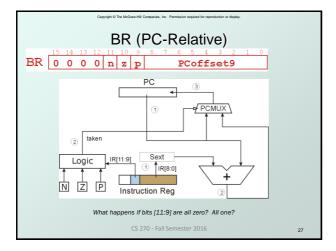

# Copyright @ The McGraw-Hill Companies. Inc. Permission required for reproduction or display PC-Relative Addressing Mode • Want to specify address directly in the instruction But an address is 16 bits, and so is an instruction! After subtracting 4 bits for opcode and 3 bits for register, we have 9 bits available for address. Solution: • Use the 9 bits as a signed offset from the current PC. • 9 bits: $-256 \le offset \le +255$ • Can form address such that: $PC - 256 \le X \le PC + 255$ Remember that PC is incremented as part of the FETCH phase; This is done <u>before</u> the EVALUATE ADDRESS stage.

CS 270 - Fall Semester 2016

12

|         |         |                                        |           | Copy | right © | The M | cGraw- | HII Co | mpanie | as, Inc | . Perm | ission | equire | d for re | produc | tion or | display.                                    |

|---------|---------|----------------------------------------|-----------|------|---------|-------|--------|--------|--------|---------|--------|--------|--------|----------|--------|---------|---------------------------------------------|

|         | Example |                                        |           |      |         |       |        |        |        |         |        |        |        |          |        |         |                                             |

| Address |         |                                        |           |      |         |       | In     | stru   | ıct    | ion     |        |        |        |          |        |         | Comments                                    |

| x30F6   | 1       | <b>1 1 1 0</b> 0 0 1 1 1 1 1 1 1 1 0 1 |           |      |         |       |        |        |        |         |        |        |        |          |        |         | R1 ← PC - 3 = x30F4                         |

| x30F7   | 0       | 0                                      | 0         | 1    | 0       | 1     | 0      | 0      | 0      | 1       | 1      | 0      | 1      | 1        | 1      | 0       | R2 ← R1 + 14 = x3102                        |

| x30F8   | 0       | 0                                      | 1         | 1    | 0       | 1     | 0      | 1      | 1      | 1       | 1      | 1      | 1      | 0        | 1      | 1       | M[PC - 5] ← R2<br>M[x30F4] ← x3102          |

| x30F9   | 0       | 1                                      | 0         | 1    | 0       | 1     | 0      | 0      | 1      | 0       | 1      | 0      | 0      | 0        | 0      | 0       | R2 ← 0                                      |

| x30FA   | 0       | 0                                      | 0         | 1    | 0       | 1     | 0      | 0      | 1      | 0       | 1      | 0      | 0      | 1        | 0      | 1       | R2 ← R2 + 5 = 5                             |

| x30FB   | 0       | 1                                      | 1         | 1    | 0       | 1     | 0      | 0      | 0      | 1       | 0      | 0      | 1      | 1        | 1      | 0       | M[R1+14] ← R2<br>M[x3102] ← 5               |

| x30FC   | 1       | 0<br>opc                               | 1<br>code | 0    | 0       | 1     | 1      | 1      | 1      | 1       | 1      | 1      | 0      | 1        | 1      | 1       | R3 ← M[M[x30F4]]<br>R3 ← M[x3102]<br>R3 ← 5 |

|         |         |                                        |           |      |         |       | CS     | 5 27   | 0 - F  | all     | Sem    | este   | er 20  | 016      |        |         | 23                                          |

|                |   |   |   | Сору | right ⊂ | The N | loGraw | HIC  | ompani | ies, Inc | . Pern | nission | requin | ad for r | eprodu | ction o | ar display.               |

|----------------|---|---|---|------|---------|-------|--------|------|--------|----------|--------|---------|--------|----------|--------|---------|---------------------------|

| Sample Program |   |   |   |      |         |       |        |      |        |          |        |         |        |          |        |         |                           |

| Address        |   |   |   |      |         |       | In     | stru | ıcti   | ion      |        |         |        |          |        |         | Comments                  |

| x3000          | 1 | 1 | 1 | 0    | 0       | 0     | 1      | 0    | 1      | 1        | 1      | 1       | 1      | 1        | 1      | 1       | R1 ← x3100 (PC+0xFF)      |

| x3001          | 0 | 1 | 0 | 1    | 0       | 1     | 1      | 0    | 1      | 1        | 1      | 0       | 0      | 0        | 0      | 0       | R3 ← 0                    |

| x3002          | 0 | 1 | 0 | 1    | 0       | 1     | 0      | 0    | 1      | 0        | 1      | 0       | 0      | 0        | 0      | 0       | R2 ← 0                    |

| x3003          | 0 | 0 | 0 | 1    | 0       | 1     | 0      | 0    | 1      | 0        | 1      | 0       | 1      | 1        | 0      | 0       | R2 ← 12                   |

| x3004          | 0 | 0 | 0 | 0    | 0       | 1     | 0      | 0    | 0      | 0        | 0      | 0       | 0      | 1        | 0      | 1       | If Z, goto x300A (PC+5)   |

| x3005          | 0 | 1 | 1 | 0    | 1       | 0     | 0      | 0    | 0      | 1        | 0      | 0       | 0      | 0        | 0      | 0       | Load next value to R4     |

| x3006          | 0 | 0 | 0 | 1    | 0       | 1     | 1      | 0    | 1      | 1        | 0      | 0       | 0      | 0        | 0      | 1       | Add to R3                 |

| x3007          | 0 | 0 | 0 | 1    | 0       | 0     | 1      | 0    | 0      | 1        | 1      | 0       | 0      | 0        | 0      | 1       | Increment R1 (pointer)    |

| X3008          | 0 | 0 | 0 | 1    | 0       | 1     | 0      | 0    | 1      | 0        | 1      | 1       | 1      | 1        | 1      | 1       | Decrement R2<br>(counter) |

| x3009          | 0 | 0 | 0 | 0    | 1       | 1     | 1      | 1    | 1      | 1        | 1      | 1       | 1      | 0        | 1      | 0       | Goto x3004 (PC-6)         |

|                |   |   |   |      |         |       | С      | S 27 | 0 - 1  | Fall     | Sem    | nest    | er 2   | 016      |        |         | 29                        |

|                                                      | Copyright © The M     | toGraw-Hill Companies, Inc. Permission required for reproduction or display.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |  |  |  |  |  |  |  |  |  |  |  |

|------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|--|

|                                                      | TRAP                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |  |  |  |  |  |  |  |  |  |  |  |

| TRAP 1 1                                             | 13 12 1<br><b>1 1</b> | 11         10         9         8         7         6         5         4         3         2         1         0           0         0         0         0         trapvect8         1         1         0         1         0         1         0         1         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         0         1         1         0 <th1< th="">         1         0         1         1         1         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         <th1< th="">         1         1         1</th1<></th1<> |    |  |  |  |  |  |  |  |  |  |  |  |

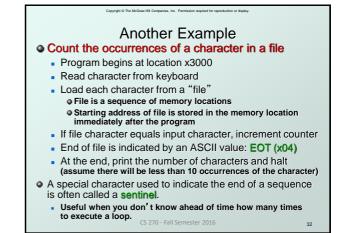

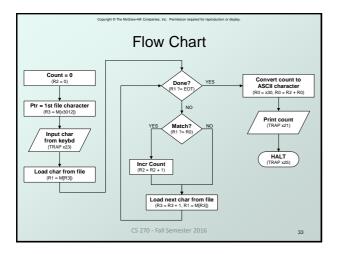

| • Calls a service routine, identified by 8-bit "trap |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |  |  |  |  |  |  |  |  |  |  |  |

| vector."                                             | vector                | routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |  |  |  |  |  |  |  |  |  |  |  |

|                                                      | x23                   | x23 input a character from the keyboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |  |  |  |  |  |  |  |  |  |  |  |

|                                                      | x21                   | output a character to the monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |  |  |  |  |  |  |  |  |  |  |  |

|                                                      | x25                   | halt the program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |  |  |  |  |  |  |  |  |  |  |  |

| • When routine is done,                              |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |  |  |  |  |  |  |  |  |  |  |  |

|                                                      |                       | instruction following TRAP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |  |  |  |  |  |  |  |  |  |  |  |

| <ul> <li>vve li taik</li> </ul>                      | about no              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |  |  |  |  |  |  |  |  |  |  |  |

|                                                      |                       | CS 270 - Fall Semester 2016 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11 |  |  |  |  |  |  |  |  |  |  |  |

|         |   |   |   | Сору | right © | The N | lcGraw | HI C | ompani | ies, Inc | . Pern | nission | requin | ad for r | eprodu | ction c | r display.             |

|---------|---|---|---|------|---------|-------|--------|------|--------|----------|--------|---------|--------|----------|--------|---------|------------------------|

|         |   |   |   |      |         | P     | rc     | g    | ra     | an       | n      | (1      |        | of       | 2      | 2)      |                        |

| Address | _ |   |   |      |         |       | In     | stru | uct    | ion      |        |         |        |          |        |         | Comments               |

| x3000   | 0 | 1 | 0 | 1    | 0       | 1     | 0      | 0    | 1      | 0        | 1      | 0       | 0      | 0        | 0      | 0       | R2 ← 0 (counter)       |

| x3001   | 0 | 0 | 1 | 0    | 0       | 1     | 1      | 0    | 0      | 0        | 0      | 1       | 0      | 0        | 0      | 0       | R3 ← M[x3102] (ptr)    |

| x3002   | 1 | 1 | 1 | 1    | 0       | 0     | 0      | 0    | 0      | 0        | 1      | 0       | 0      | 0        | 1      | 1       | Input to R0 (TRAP x23) |

| x3003   | 0 | 1 | 1 | 0    | 0       | 0     | 1      | 0    | 1      | 1        | 0      | 0       | 0      | 0        | 0      | 0       | R1 ← M[R3]             |

| x3004   | 0 | 0 | 0 | 1    | 1       | 0     | 0      | 0    | 0      | 1        | 1      | 1       | 1      | 1        | 0      | 0       | R4 ← R1 - 4 (EOT)      |

| x3005   | 0 | 0 | 0 | 0    | 0       | 1     | 0      | 0    | 0      | 0        | 0      | 0       | 1      | 0        | 0      | 0       | If Z, goto x300E       |

| x3006   | 1 | 0 | 0 | 1    | 0       | 0     | 1      | 0    | 0      | 1        | 1      | 1       | 1      | 1        | 1      | 1       | R1 ← NOT R1            |

| x3007   | 0 | 0 | 0 | 1    | 0       | 0     | 1      | 0    | 0      | 1        | 1      | 0       | 0      | 0        | 0      | 1       | R1 ← R1 + 1            |

| X3008   | 0 | 0 | 0 | 1    | 0       | 0     | 1      | 0    | 0      | 1        | 0      | 0       | 0      | 0        | 0      | 0       | R1 ← R1 + R0           |

| x3009   | 0 | 0 | 0 | 0    | 1       | 0     | 1      | 0    | 0      | 0        | 0      | 0       | 0      | 0        | 0      | 1       | If N or P, goto x300B  |

|         |   |   |   |      |         |       | С      | S 27 | 0 -    | Fall     | Sem    | nest    | er 2   | 016      |        |         | 34                     |

| Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display. |                  |   |    |    |    |    |     |      |       |       |     |      |       |     |   |   |                     |

|----------------------------------------------------------------------------------------------|------------------|---|----|----|----|----|-----|------|-------|-------|-----|------|-------|-----|---|---|---------------------|

|                                                                                              | Program (2 of 2) |   |    |    |    |    |     |      |       |       |     |      |       |     |   |   |                     |

| Address                                                                                      |                  |   |    |    |    |    | Ins | stru | ıcti  | ion   |     |      |       |     |   |   | Comments            |

| x300A                                                                                        | 0                | 0 | 0  | 1  | 0  | 1  | 0   | 0    | 1     | 0     | 1   | 0    | 0     | 0   | 0 | 1 | R2 ← R2 + 1         |

| x300B                                                                                        | 0                | 0 | 0  | 1  | 0  | 1  | 1   | 0    | 1     | 1     | 1   | 0    | 0     | 0   | 0 | 1 | R3 ← R3 + 1         |

| x300C                                                                                        | 0                | 1 | 1  | 0  | 0  | 0  | 1   | 0    | 1     | 1     | 0   | 0    | 0     | 0   | 0 | 0 | R1 ← M[R3]          |

| x300D                                                                                        | 0                | 0 | 0  | 0  | 1  | 1  | 1   | 1    | 1     | 1     | 1   | 1    | 0     | 1   | 1 | 0 | Goto x3004          |

| x300E                                                                                        | 0                | 0 | 1  | 0  | 0  | 0  | 0   | 0    | 0     | 0     | 0   | 0    | 0     | 1   | 0 | 0 | R0 ← M[x3013]       |

| x300F                                                                                        | 0                | 0 | 0  | 1  | 0  | 0  | 0   | 0    | 0     | 0     | 0   | 0    | 0     | 0   | 1 | 0 | R0 ← R0 + R2        |

| x3010                                                                                        | 1                | 1 | 1  | 1  | 0  | 0  | 0   | 0    | 0     | 0     | 1   | 0    | 0     | 0   | 0 | 1 | Print R0 (TRAP x21) |

| x3011                                                                                        | 1                | 1 | 1  | 1  | 0  | 0  | 0   | 0    | 0     | 0     | 1   | 0    | 0     | 1   | 0 | 1 | HALT (TRAP x25)     |

| X3012                                                                                        |                  |   | St | ar | ti | ng | A   | dd   | re    | ss    | 0   | f    | Fi    | le  |   |   |                     |

| x3013                                                                                        | 0                | 0 | 0  | 0  | 0  | 0  | 0   | 0    | 0     | 0     | 1   | 1    | 0     | 0   | 0 | 0 | ASCII x30 ( '0')    |

|                                                                                              |                  |   |    |    |    |    | CS  | 270  | ) - F | all S | iem | este | er 20 | 016 |   |   | 35                  |

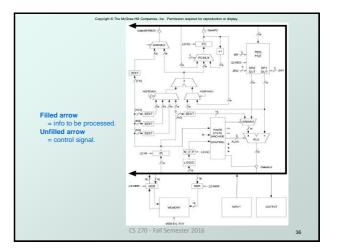

# Data Path Components

#### Global bus

- special set of wires that carry a 16-bit signal to many components

- inputs to the bus are "tri-state devices", that only place a signal on the bus when they are enabled

- only one (16-bit) signal should be enabled at any time o control unit decides which signal "drives" the bus

- any number of components can read the bus

- register only captures bus data if it is write-enabled by the control unit

#### Memory

- Control and data registers for memory and I/O devices

- memory: MAR, MDR (also control signal for read/write) CS 270 - Fall Semester 2016

37

# Data Path Components

### ALU

- Accepts inputs from register file

- and from sign-extended bits from IR (immediate field). Output goes to bus.

- used by condition code logic, register file, memory Register File

- Two read addresses (SR1, SR2), one write address (DR)

- Input from bus

- result of ALU operation or memory read Two 16-bit outputs

- used by ALU, PC, memory address • data for store instructions passes through ALU

# right © The McGraw Hill Companies Inc. Remission maximal for momentation or der Data Path Components

## PC and PCMUX

- Three inputs to PC, controlled by PCMUX

- 1.PC+1 FETCH stage

- 2.Address adder BR, JMP

- 3.bus TRAP (discussed later)

#### MAR and MARMUX

- Two inputs to MAR, controlled by MARMUX

- 1.Address adder LD/ST, LDR/STR

- 2.Zero-extended IR[7:0] -- TRAP (discussed later)

CS 270 - Fall Semester 2016

Copyright @ The McGraw-Hill Companies. Inc. Permission required for reproduction or display

# Data Path Components

- Condition Code Logic

- Looks at value on bus and generates N, Z, P signals

- Registers set only when control unit enables them (LD.CC) only certain instructions set the codes (ADD, AND, NOT, LD, LDI, LDR, LEA)

### Control Unit – Finite State Machine

- On each machine cycle, changes control signals for next phase of instruction processing

- who drives the bus? (GatePC, GateALU, ...)

- which registers are write enabled? (LD.IR, LD.REG, ...)

- which operation should ALU perform? (ALUK)

- Logic includes decoder for opcode, etc.

CS 270 - Fall Semester 2016

40