## I/O: Connecting to Outside World

wight © The McGraw-Hill Companies. Inc. Permission required for reproduction or displa

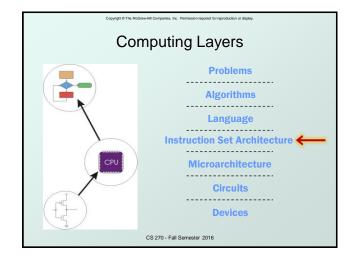

• So far, we've learned how to:

- compute with values in registers

- load data from memory to registers

- store data from registers to memory

- But where does data in memory come from?

- And how does data get out of the system so that humans can use it?

CS 270 - Fall Semester 2016

## Copyrigt & The McGraw-HII Comparise, Inc. Permission required for reproduction or depa Transfer Control

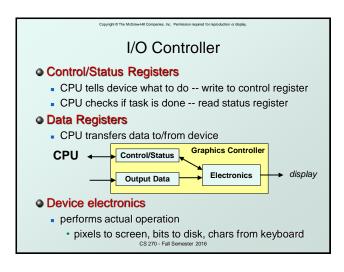

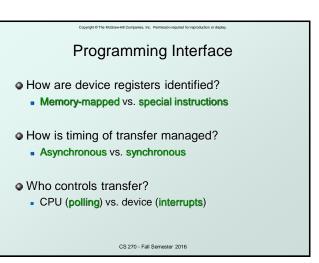

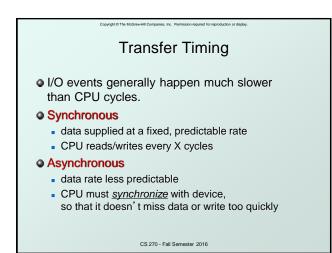

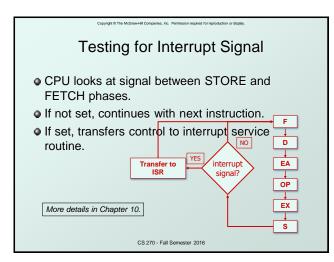

• Who determines when the next data transfer occurs?

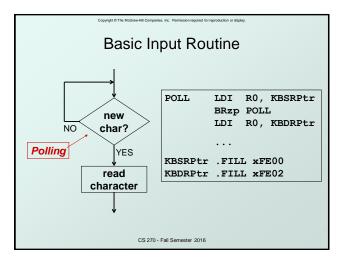

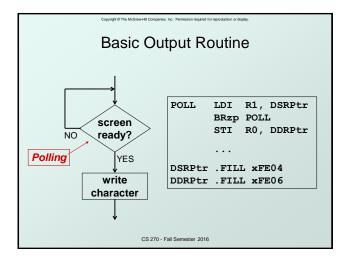

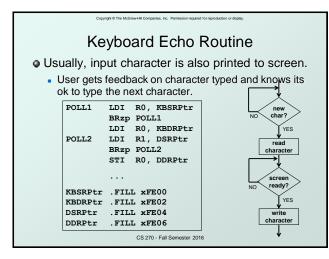

## Polling

- CPU keeps checking status register until <u>new data</u> arrives OR <u>device ready</u> for next data

- "Are we there yet? Are we there yet? Are we ...

### Interrupts

- Device sends a special signal to CPU when <u>new data</u> arrives OR <u>device ready</u> for next data

- CPU can be performing other tasks instead of polling device.

- Wake me when we get there." CS 270 - Fall Semester 2016

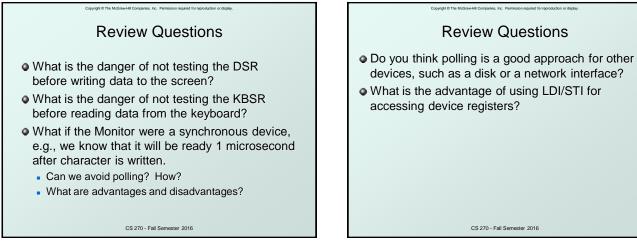

##

Copyright @ The McGraw-Hill Companies, Inc. Permission required for reproduction or displa

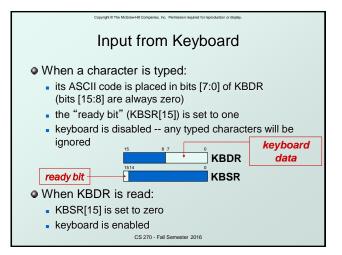

|  | Location | I/O Register              | Function                                                        |

|--|----------|---------------------------|-----------------------------------------------------------------|

|  | xFE00    | Keyboard Status<br>(KBSR) | Bit [15] is one when keyboard has received a new character.     |

|  | xFE02    | Keyboard Data (KBDR)      | Bits [7:0] contain the last character typed on keyboard.        |

|  | xFE04    | Display Status (DSR)      | Bit [15] is one when device ready to display char on screen.    |

|  | xFE06    | Display Data (DDR)        | Character written to bits [7:0] will<br>be displayed on screen. |

## Asynchronous devices

synchronized through status registers

#### Polling and Interrupts

Interrupt details will be discussed in Chapter 10

CS 270 - Fall Semester 2016

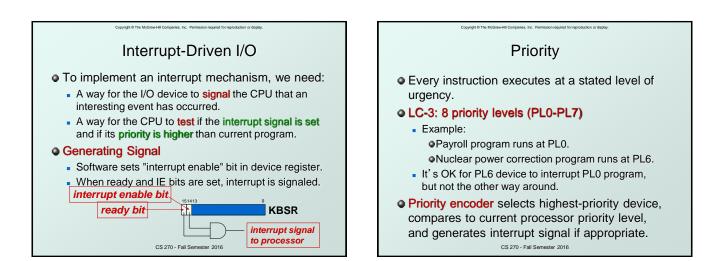

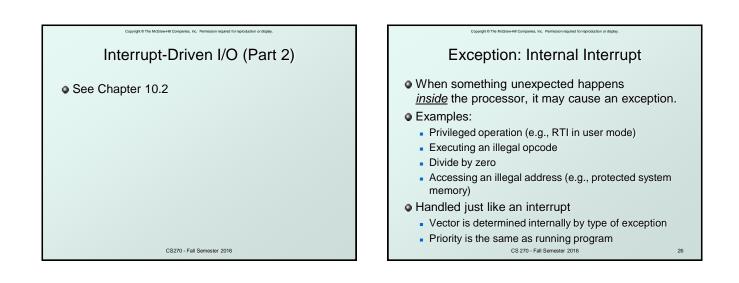

## Interrupt-Driven I/O

- External device can:

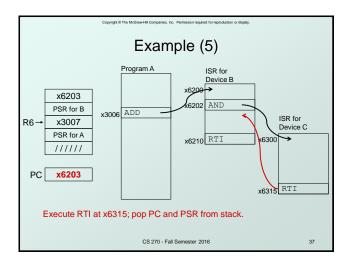

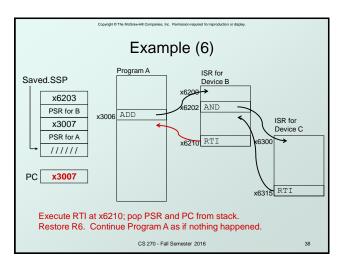

- (1) Force currently executing program to stop.

Convicte O The McGraw-Hill Companies Inc. Pe

- (2) Have the processor satisfy the device needs.

- (3) Resume the program as if nothing happened.

- Why?

- Polling consumes a lot of cycles, especially for rare events – these cycles can be used for more computation.

- I/O device is faster than the CPU.

- Example: Process previous input while collecting current input. (See Example 8.1 in text.)

CS 270 - Fall Semester 2016

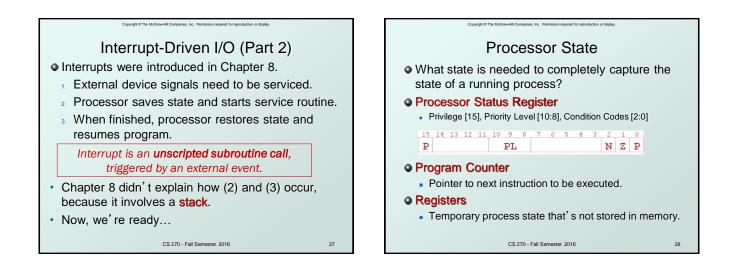

## Where to Save Processor State?

#### Can't use registers.

- Programmer doesn't know when interrupt might occur, so she can't prepare by saving critical registers.

- When resuming, need to restore state exactly as it was.

- Memory allocated by service routine?

- Must save state <u>before</u> invoking routine, so we wouldn't know where.

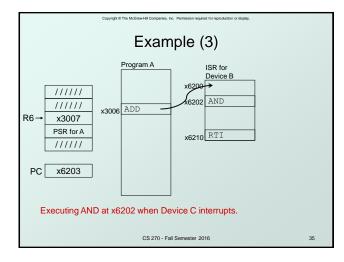

- Also, interrupts may be nested that is, an interrupt service routine might also get interrupted!

CS 270 - Fall Semester 2016

#### • Use a stack!

- Location of stack "hard-wired".

- Push state to save, pop to restore.

20

31

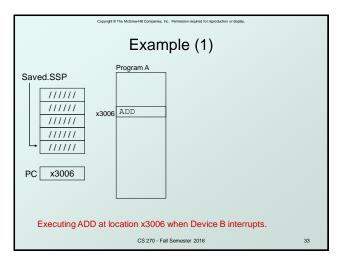

# Supervisor Stack

- A special region of memory used as the stack for interrupt service routines.

- Initial Supervisor Stack Pointer (SSP) stored in Saved.SSP.

- Another register for storing User Stack Pointer (USP): Saved.USP.

- Want to use R6 as stack pointer.

- So that our PUSH/POP routines still work.

- When switching from User mode to Supervisor mode (as result of interrupt), save R6 to Saved.USP.

CS 270 - Fall Semester 2016

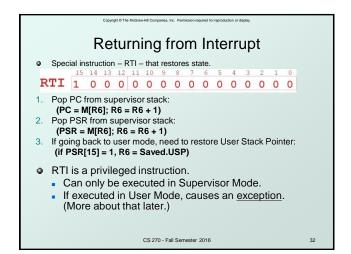

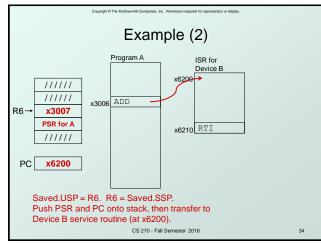

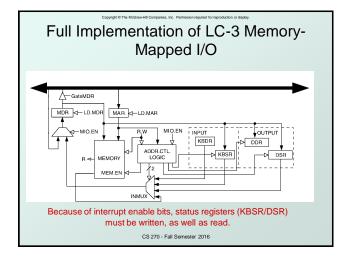

## Invoking the Service Routine (Details)

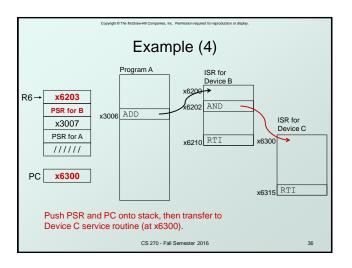

- 1. If Priv = 1 (user), Saved.USP = R6, then R6 = Saved.SSP.

- 2. Push PSR and PC to Supervisor Stack.

- 3. Set **PSR[15]** = 0 (supervisor mode).

- 4. Set **PSR[10:8]** = priority of interrupt being serviced.

- 5. Set **PSR[2:0]** = 0.

- Set MAR = x01vv, where vv = 8-bit interrupt vector provided by interrupting device (e.g., keyboard = x80).

- 7. Load memory location (M[x01vv]) into MDR.

- Set PC = MDR; now first instruction of ISR will be fetched.

Note: This all happens between

the STORE RESULT of the last user instruction and the FETCH of the first ISR instruction.