# Grapter 5 B

#### Parallel Processors from Client to Cloud

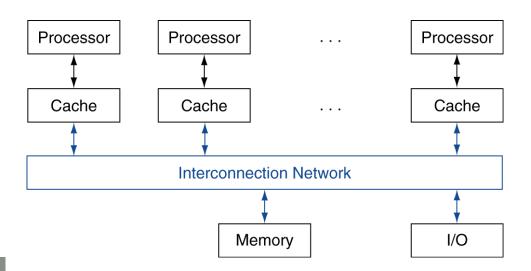

# **Shared Memory**

- SMP: shared memory multiprocessor

- Hardware provides single physical address space for all processors

- Synchronize shared variables using locks

- Memory access time

- UMA (uniform) vs. NUMA (nonuniform)

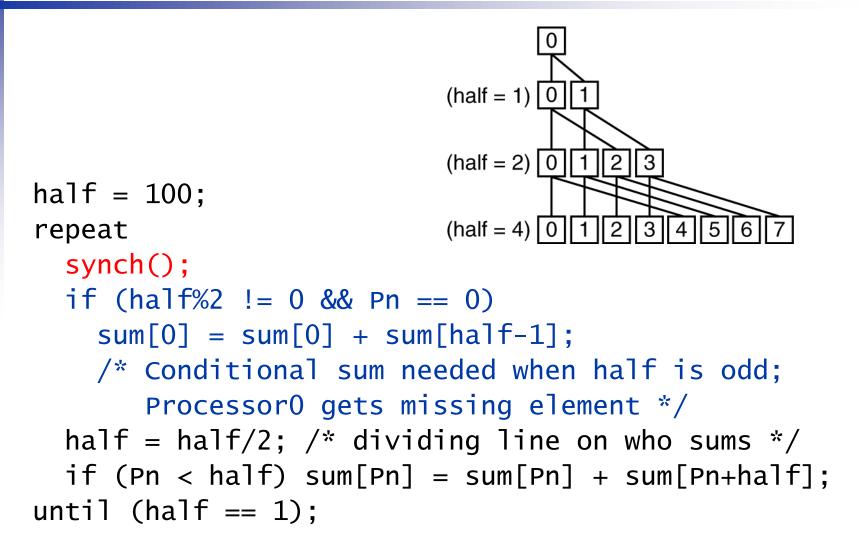

# **Example: Sum Reduction**

- Sum 100,000 numbers on 100 processor UMA

- Each processor has ID:  $0 \le Pn \le 99$

- Partition 1000 numbers per processor

- Initial summation on each processor

- Now need to add these partial sums

- Reduction: divide and conquer

- Half the processors add pairs, then quarter, ...

- Need to synchronize between reduction steps

#### **Example: Sum Reduction**

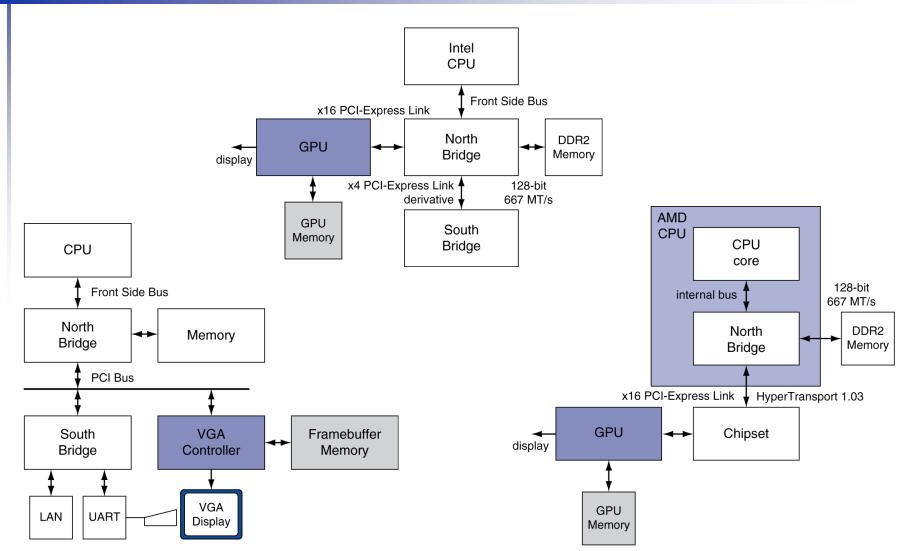

# **History of GPUs**

- Early video cards

- Frame buffer memory with address generation for video output

- 3D graphics processing

- Originally high-end computers (e.g., SGI)

- Moore's Law  $\Rightarrow$  lower cost, higher density

- 3D graphics cards for PCs and game consoles

- Graphics Processing Units

- Processors oriented to 3D graphics tasks

- Vertex/pixel processing, shading, texture mapping, rasterization

## **Graphics in the System**

#### Chapter 6 — Parallel Processors from Client to Cloud — 6

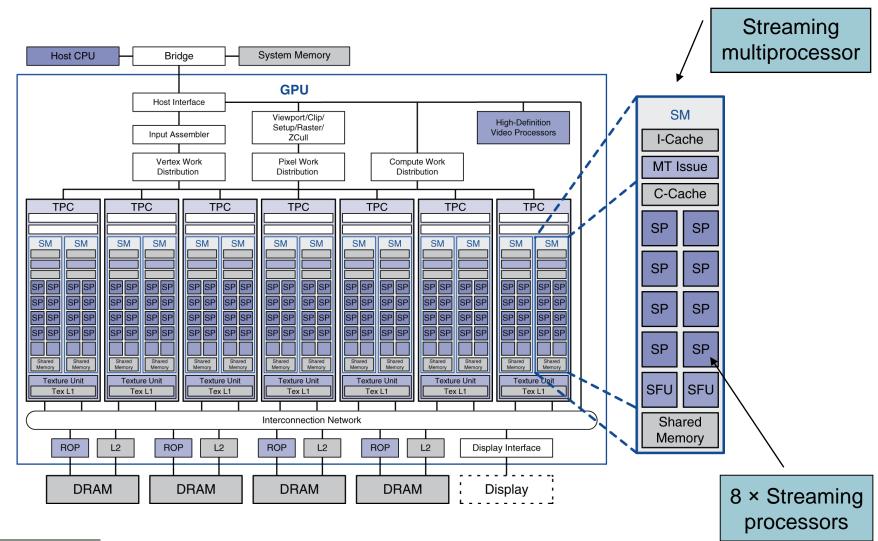

# **GPU Architectures**

- Processing is highly data-parallel

- GPUs are highly multithreaded

- Use thread switching to hide memory latency

Less reliance on multi-level caches

- Graphics memory is wide and high-bandwidth

- Trend toward general purpose GPUs

- Heterogeneous CPU/GPU systems

- CPU for sequential code, GPU for parallel code

- Programming languages/APIs

- DirectX, OpenGL

- C for Graphics (Cg), High Level Shader Language (HLSL)

- Compute Unified Device Architecture (CUDA)

### **Example: NVIDIA Tesla**

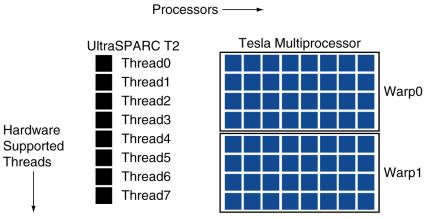

# **Example: NVIDIA Tesla**

- **Streaming Processors**

- Single-precision FP and integer units

- Each SP is fine-grained multithreaded

- Warp: group of 32 threads

- Executed in parallel, SIMD style

- 8 SPs x 4 clock cy

- × 4 clock cycles

- Hardware contexts for 24 warps

- Registers, PCs, …

# **Classifying GPUs**

#### Don't fit nicely into SIMD/MIMD model

- Conditional execution in a thread allows an illusion of MIMD

- But with performance degredation

- Need to write general purpose code with care

|                                  | Static: Discovered<br>at Compile Time | Dynamic: Discovered<br>at Runtime |

|----------------------------------|---------------------------------------|-----------------------------------|

| Instruction-Level<br>Parallelism | VLIW                                  | Superscalar                       |

| Data-Level<br>Parallelism        | SIMD or Vector                        | Tesla Multiprocessor              |

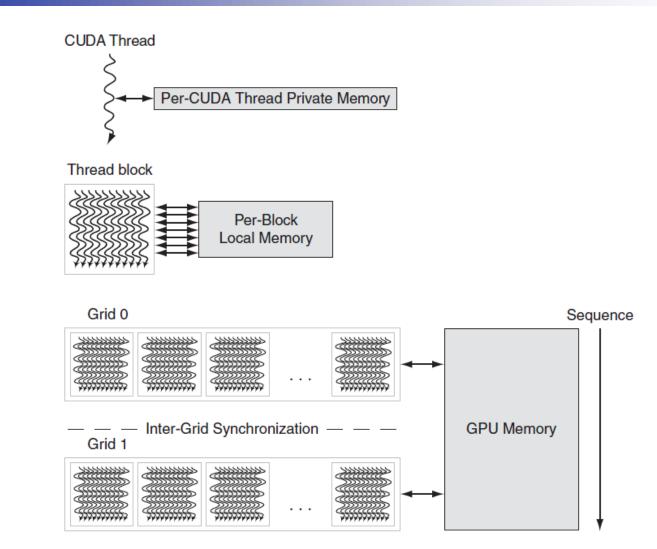

## **GPU Memory Structures**

### **Putting GPUs into Perspective**

| Feature                                                           | Multicore with SIMD | GPU          |  |

|-------------------------------------------------------------------|---------------------|--------------|--|

| SIMD processors                                                   | 4 to 8              | 8 to 16      |  |

| SIMD lanes/processor                                              | 2 to 4              | 8 to 16      |  |

| Multithreading hardware support for SIMD threads                  | 2 to 4              | 16 to 32     |  |

| Typical ratio of single precision to double-precision performance | 2:1                 | 2:1          |  |

| Largest cache size                                                | 8 MB                | 0.75 MB      |  |

| Size of memory address                                            | 64-bit              | 64-bit       |  |

| Size of main memory                                               | 8 GB to 256 GB      | 4 GB to 6 GB |  |

| Memory protection at level of page                                | Yes                 | Yes          |  |

| Demand paging                                                     | Yes                 | No           |  |

| Integrated scalar processor/SIMD processor                        | Yes                 | No           |  |

| Cache coherent                                                    | Yes                 | No           |  |

#### **Guide to GPU Terms**

| Туре                 | More descriptive<br>name               | Closest old term<br>outside of GPUs           | Official CUDA/<br>NVIDIA GPU term | Book definition                                                                                                                                                             |  |

|----------------------|----------------------------------------|-----------------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Program abstractions | Vectorizable<br>Loop                   | Vectorizable Loop                             | Grid                              | A vectorizable loop, executed on the GPU, made<br>up of one or more Thread Blocks (bodies of<br>vectorized loop) that can execute in parallel.                              |  |

|                      | Body of<br>Vectorized Loop             | Body of a<br>(Strip-Mined)<br>Vectorized Loop | Thread Block                      | A vectorized loop executed on a multithreaded<br>SIMD Processor, made up of one or more threads<br>of SIMD instructions. They can communicate via<br>Local Memory.          |  |

|                      | Sequence of<br>SIMD Lane<br>Operations | One iteration of<br>a Scalar Loop             | CUDA Thread                       | A vertical cut of a thread of SIMD instructions<br>corresponding to one element executed by one<br>SIMD Lane. Result is stored depending on mask<br>and predicate register. |  |

| Machine object       | A Thread of<br>SIMD<br>Instructions    | Thread of Vector<br>Instructions              | Warp                              | A traditional thread, but it contains just SIMD<br>instructions that are executed on a multithreaded<br>SIMD Processor. Results stored depending on a<br>per-element mask.  |  |

| Mach                 | SIMD<br>Instruction                    | Vector Instruction                            | PTX Instruction                   | A single SIMD instruction executed across SIMD<br>Lanes.                                                                                                                    |  |

| Processing hardware  | Multithreaded<br>SIMD<br>Processor     | (Multithreaded)<br>Vector Processor           | Streaming<br>Multiprocessor       | A multithreaded SIMD Processor executes<br>threads of SIMD instructions, independent of<br>other SIMD Processors.                                                           |  |

|                      | Thread Block<br>Scheduler              | Scalar Processor                              | Giga Thread<br>Engine             | Assigns multiple Thread Blocks (bodies of<br>vectorized loop) to multithreaded SIMD<br>Processors.                                                                          |  |

|                      | SIMD Thread<br>Scheduler               | Thread scheduler<br>in a Multithreaded<br>CPU | Warp Scheduler                    | Hardware unit that schedules and issues threads<br>of SIMD instructions when they are ready to<br>execute; includes a scoreboard to track SIMD<br>Thread execution.         |  |

|                      | SIMD Lane                              | Vector lane                                   | Thread Processor                  | A SIMD Lane executes the operations in a thread<br>of SIMD instructions on a single element. Results<br>stored depending on mask.                                           |  |

| Memory hardware      | GPU Memory                             | Main Memory                                   | Global Memory                     | DRAM memory accessible by all multithreaded<br>SIMD Processors in a GPU.                                                                                                    |  |

|                      | Local Memory                           | Local Memory                                  | Shared Memory                     | Fast local SRAM for one multithreaded SIMD<br>Processor, unavailable to other SIMD Processors.                                                                              |  |

| Mer                  | SIMD Lane<br>Registers                 | Vector Lane<br>Registers                      | Thread Processor<br>Registers     | Registers in a single SIMD Lane allocated across<br>a full thread block (body of vectorized loop).                                                                          |  |

#### i7-960 vs. NVIDIA Tesla 280/480

|                                                | Core i7-<br>960 | GTX 280    | GTX 480     | <b>Ratio</b><br>280/i7 | Ratio<br>480/17 |

|------------------------------------------------|-----------------|------------|-------------|------------------------|-----------------|

| Number of processing elements (cores or SMs)   | 4               | 30         | 15          | 7.5                    | 3.8             |

| Clock frequency (GHz)                          | 3.2             | 1.3        | 1.4         | 0.41                   | 0.44            |

| Die size                                       | 263             | 576        | 520         | 2.2                    | 2.0             |

| Technology                                     | Intel 45 nm     | TCMS 65 nm | TCMS 40 nm  | 1.6                    | 1.0             |

| Power (chip, not module)                       | 130             | 130        | 167         | 1.0                    | 1.3             |

| Transistors                                    | 700 M           | 1400 M     | 3100 M      | 2.0                    | 4.4             |

| Memory brandwith (GBytes/sec)                  | 32              | 141        | 177         | 4.4                    | 5.5             |

| Single frecision SIMD width                    | 4               | 8          | 32          | 2.0                    | 8.0             |

| Dobule precision SIMD with                     | 2               | 1          | 16          | 0.5                    | 8.0             |

| Peak Single frecision scalar FLOPS (GFLOP/sec) | 26              | 117        | 63          | 4.6                    | 2.5             |

| Peak Single frecision s SIMD FLOPS (GFLOP/Sec) | 102             | 311 to 933 | 515 to 1344 | 3.0-9.1                | 6.6-13.1        |

| (SP 1 add or multiply)                         | N.A.            | (311)      | (515)       | (3.0)                  | (6.6)           |

| (SP 1 instruction fused)                       | N.A             | (622)      | (1344)      | (6.1)                  | (13.1)          |

| (face SP dual issue fused)                     | N.A             | (933)      | N.A         | (9.1)                  | -               |

| Peal double frecision SIMD FLOPS (GFLOP/sec)   | 51              | 78         | 515         | 1.5                    | 10.1            |

### **Pitfalls**

- Not developing the software to take account of a multiprocessor architecture

- Example: using a single lock for a shared composite resource

- Serializes accesses, even if they could be done in parallel

- Use finer-granularity locking

# **Concluding Remarks**

- Goal: higher performance by using multiple processors

- Difficulties

- Developing parallel software

- Devising appropriate architectures

- SaaS importance is growing and clusters are a good match

- Performance per dollar and performance per Joule drive both mobile and WSC